Namun, menggunakan atau men-debug DAC / ADC bisa jadi sulit karena batasan yang ditetapkan oleh produsen perangkat keras, misalnya, pada perangkat lunak yang digunakan atau bagaimana perangkat dapat dikontrol. Ini menyarankan untuk merancang model interaksi Anda sendiri.

Pada artikel ini kami akan mempertimbangkan kemungkinan mengatur interaksi antara PC dan DAC / ADC menggunakan FPGA.

Kata pengantar

Tujuan utama artikel ini adalah untuk menjelaskan solusi untuk masalah tertentu, serta keakraban dengan antarmuka interaksi sirkuit terintegrasi (IC). Tujuan utama DAC / ADC tidak dibahas di sini.

Artikel ini memerlukan beberapa pengetahuan tentang pemrograman dan sirkuit berorientasi objek, jadi jika Anda tidak terbiasa dengan konsep-konsep ini, disarankan untuk memulainya.

Saya berharap pengalaman seseorang yang pertama kali menghadapi masalah komunikasi perangkat elektronik akan bermanfaat bagi seseorang.

Semoga sukses dan prestasi baru untuk semuanya!

Program pendidikan kecil di antarmuka

Penolakan

Jika Anda terbiasa dengan struktur antarmuka utama yang digunakan untuk komunikasi IC, Anda dapat melewati poin ini dengan aman.

program pendidikan

, .

, (, .) . , .

, . , , , .. , . . – , . , . , .

, .

( ), :

«-» — , . , — .

«» (, « » «») , . . , , , . .

( «») . , , , - . .

:

, . . . , .

, . , , .

(-/)

:

. .

, .

: , «» .

. .

:

. . . ( – , – , , ). « » ( ). .

, , .

() SPI I2C UART.

I2C – . I2C . I2C «-», .

, , . , . 7- 16 . , 112 . I2C (SDA) (SCL).

I2C

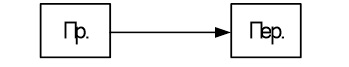

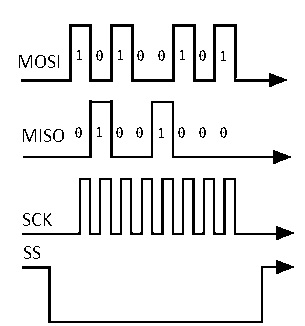

SPI – , .

SPI «-». MOSI SCLK, . MISO, . SS.

SPI

UART – – , .

RxD ( ) TxD ( ).

UART TxD . . UART , , UART , . , . 8 ( ), , .

UART «-». , UART . « » «».

UART

, .

, (, .) . , .

, . , , , .. , . . – , . , . , .

, .

( ), :

- «-»;

- «»;

- «» («»).

«-» — , . , — .

«» (, « » «») , . . , , , . .

( «») . , , , - . .

:

- ;

- ;

- -.

, . . . , .

, . , , .

(-/)

:

- ();

- ();

- ().

. .

, .

: , «» .

. .

:

- ;

- .

. . . ( – , – , , ). « » ( ). .

, , .

?

() SPI I2C UART.

I2C

I2C – . I2C . I2C «-», .

, , . , . 7- 16 . , 112 . I2C (SDA) (SCL).

I2C

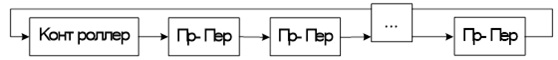

SPI

SPI – , .

SPI «-». MOSI SCLK, . MISO, . SS.

SPI

UART

UART – – , .

RxD ( ) TxD ( ).

UART TxD . . UART , , UART , . , . 8 ( ), , .

UART «-». , UART . « » «».

UART

Apa DAC ini?

Tampaknya bukan yang ini

Pertama, mari kita definisikan DAC / ADC yang digunakan:

Papan debug Analog Devices AD9993-EBZ adalah perangkat yang menggabungkan empat ADC 14-bit dan dua DAC 14-bit.

Mode operasi IC ini dikontrol dengan mengubah status register internalnya. AD9993 menggunakan 66 register dengan ukuran word yang disimpan (diproses) 8 bit, yang alamatnya dijelaskan oleh nilai heksadesimal tiga digit (12 bit data). Dua jenis perintah didukung - perintah baca dan perintah tulis. Dengan kata lain, untuk mengoreksi pengoperasian IC, perlu mengirim perintah untuk menulis nilai 8-bit yang valid ke alamat register tertentu. Akses ke register IC ini dilakukan melalui antarmuka periferal serial (SPI), koneksi yang pada papan debug direalisasikan melalui konektor 40-pin FIFO_0 atau melalui grup kontak tambahan yang dipasang.

Seperti yang ini (FIFO_0 - konektor abu-abu atas)

Persyaratan dasar untuk parameter batas SPI:

- Frekuensi transmisi data maksimum - 25 MHz;

- Durasi level atas dan bawah pada jalur penghasil sinyal sinkronisasi adalah 10 ns;

- Waktu pengaturan level pada jalur transmisi data dan pada jalur resolusi - 2 ns;

- Level tahan waktu pada jalur transmisi data dan pada jalur resolusi - 2 ns;

- Waktu yang dijamin validitas dari satu bit data pada jalur transmisi slave adalah 2 ns.

Penjelasan lengkap tentang fitur perangkat dapat ditemukan dalam dokumentasinya .

Apa kata pabrikan?

Skema kontrol yang direkomendasikan

Berdasarkan dokumentasi AD9993-EBZ, cara yang disarankan untuk mengontrol IC adalah dengan menggunakan papan debug Perangkat Analog HSC-ADC-EVALC yang terhubung ke IC melalui port 40-pin dan ke PC melalui antarmuka USB.

SPIController digunakan sebagai perangkat lunak kontrol. Perangkat Analog yang

Direkomendasikan

Sirkuit HSC-ADC-EVALC (berdasarkan Xilinx Virtex-4 FPGA)

kontra:

- Harga tinggi. Papan debug HSC-ADC-EVALC di situs resmi Analog Devices ditawarkan seharga $ 698,28.

- Antarmuka pengguna yang tidak nyaman. Software SPIController, selain fungsi utama menulis dan membaca register, tidak menyediakan kemampuan untuk menyimpan atau menjadwalkan awal perintah.

- . SPI SPIController, . Analog Devices, SPI.

SPIController

:

- .

HSC-ADC-EVALC

Perlu dicatat bahwa penggunaan board Analog Devices HSC-ADC-EVALC sebagai perangkat kontrol DAC / ADC bukanlah tujuan utamanya.

HSC-ADC-EVALC terutama digunakan sebagai kartu memori penyangga untuk ADC, namun juga memiliki fungsi untuk mengkonfigurasi kartu debug melalui SPI jika kartu yang terhubung mendukungnya.

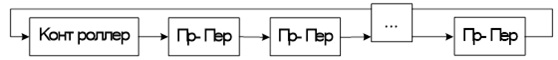

Model interaksinya sendiri

Alasan menggunakan perangkat perantara

Jelas bahwa interaksi antara DAC / ADC dan PC tidak dapat diatur secara langsung, karena SPI, yang digunakan untuk memprogram AD9993-EBZ, bukanlah antarmuka khas PC modern.

Untuk mengatasi masalah ini, perlu menggunakan perangkat perantara yang akan mengkonversi data dari antarmuka USB yang dikirim dari komputer ke format antarmuka SPI yang didukung oleh IC.

Selama menentukan opsi, pilihan jatuh pada penggunaan papan debug Terasic DE10-Nano, berdasarkan pada Cyclone V. FPGA.

Model interaksi sendiri

Mengapa FPGA sangat keren?

Keuntungan utama menggunakan FPGA:

- . DE10-Nano , , , . IDE, Verilog.

- . DE10-Nano HSC-ADC-EVALC ($110 $698.28). DE10-Nano , .

- . , .

- . FPGA- (FPGA – field-programmable gate array – , ), ( ). rocketboards c .

...

Selama desain model interaksi, diputuskan untuk mengimplementasikan antarmuka SPI berdasarkan GPIO (pin tujuan umum), yang basis kontaknya tersedia pada DE10-Nano. Implementasi pengontrol SPI berbasis FPGA seharusnya tidak menimbulkan masalah khusus karena banyaknya material pada topik yang sama.

Namun, implementasi menghubungkan FPGA ke komputer melalui antarmuka USB menyebabkan kesulitan.

DE10-Nano memiliki port USB berikut:

- USB mini-B didukung oleh chip FT232R, mewujudkan koneksi UART ke USB.

- USB mini-B dikontrol oleh chip SMSC USB3300, yang mengimplementasikan lapisan fisik antarmuka USB, serta digunakan untuk pemrograman FPGA.

Penggunaan port ini diperumit oleh fakta bahwa DE10-Nano berkomunikasi dengan port ini melalui apa yang disebut HPS ( sistem prosesor keras ) - bagian dari chip Cylone V, yang berisi modul mikroprosesor, prosesor ARM Cortex, pengontrol memori flash, dan banyak lagi. Perbedaan utama antara HPS dan FPGA adalah bahwa HPS adalah blok struktur yang tidak berubah-ubah, dioptimalkan untuk fungsi tertentu dan tidak memiliki alat pemrogramannya (dan karenanya sulit).

Bagian HPS dan FPGA dari chip Cyclone V memiliki pinnya sendiri. Pin ini tidak dibagikan secara bebas antara HPS dan FPGA. Kontak HPS dikonfigurasi oleh perangkat lunak yang berjalan di HPS. Pin FPGA diprogram menggunakan gambar konfigurasi FPGA melalui HPS atau sumber eksternal lain yang didukung.

Untuk mengatur interaksi logika terprogram dari chip Cyclone V dengan port-port ini, perlu untuk membuat bootloader Linux khusus yang berjalan pada HPS, dan juga perlu untuk mengembangkan program yang mampu mentransmisikan sinyal dari pengontrol port USB yang tersedia ke kontak bebas FPGA.

Pada tahap pengetahuan saat ini, pertanyaan ini ternyata sangat banyak, sehingga diputuskan untuk mencari cara lain. Namun, bagi orang-orang yang menghadapi masalah serupa dan memutuskan untuk mengetahuinya, mungkin berguna untuk membaca artikel tentang solusi yang mungkin.

Ada jalan keluar!

Setelah menjelajahi Internet secara menyeluruh, diputuskan untuk menggunakan pengontrol UART eksternal.

Pengontrol UART eksternal adalah papan kecil yang didasarkan pada chip FT232RL. Papan memiliki konektor miniUSB-B untuk komunikasi dengan komputer dan konektor 6-pin untuk komunikasi dengan mikrokontroler dan perangkat.

Pengontrol terhubung melalui antarmuka USB ke PC, dan melalui basis kontak GPIO ke DE10-Nano.

Pengontrol itu sendiri dari Waveshare (digunakan dalam proyek)

Menggunakan antarmuka UART melalui USB untuk mentransfer data dari PC secara virtual menghilangkan kebutuhan untuk berurusan dengan perangkat protokol USB yang kompleks dan berlapis-lapis. Mulai sekarang, interaksi melalui antarmuka USB tidak lagi menjadi perhatian kami, karena tugas ini ditetapkan ke driver yang sudah diinstal sebelumnya di sistem atau diinstal secara independen oleh pengguna.

Selain jalur listrik dan arde, serta jalur transmisi dan penerimaan data, ada pin di papan, yang ditandatangani sebagai RTS dan CTS. Kontak ini digunakan untuk apa yang disebut kontrol aliran - mekanisme yang dirancang untuk memberi sinyal kesiapan untuk menerima data dari perangkat master atau slave, tergantung pada status saluran. Penggunaan jalur ini tidak diperlukan, oleh karena itu, untuk menonaktifkan mekanisme, perlu untuk menunjukkan dalam pengaturan driver komputer bahwa kontrol aliran tidak digunakan (ini biasanya konfigurasi default).

Saat terhubung ke PC Windows, pengontrol UART terdeteksi sebagai port serial virtual. Akibatnya, pengembangan skema untuk berinteraksi dengan PC turun ke pembuatan perangkat lunak dengan fungsionalitas berinteraksi dengan port virtual serial, serta mengembangkan proyek untuk FPGA yang mengimplementasikan penerimaan / transmisi data melalui antarmuka UART.

Kontroler UART eksternal sebenarnya adalah analog absolut dari pengontrol yang sudah ada di DE10-Nano, tetapi satu-satunya keunggulannya adalah kemampuan untuk langsung menyambung ke pin bebas FPGA. Biaya perangkat semacam itu berkisar dari $ 5 hingga $ 10.

Pengembangan perangkat lunak

informasi Umum

Seperti yang telah disebutkan, pengembangan perangkat lunak untuk PC direduksi menjadi membuat program yang mendukung pertukaran informasi dengan port serial virtual. Selama analisis alat perangkat lunak yang tersedia untuk pengembangan perangkat lunak, pilihan jatuh pada bahasa pemrograman Java 8th edition menggunakan pustaka RTXT.

Java adalah bahasa pemrograman berorientasi objek yang sangat diketik dengan sejumlah fitur utama. Secara khusus, program yang ditulis dalam bahasa pemrograman Java diterjemahkan ke dalam bytecode khusus, yang memungkinkan program tersebut berjalan pada arsitektur komputer mana pun yang di dalamnya terdapat implementasi mesin virtual Java.

Pustaka standar Java tidak memiliki kemampuan untuk berinteraksi dengan port serial virtual. Untuk itulah pustaka RTXT digunakan. RTXT didistribusikan di bawah lisensi perangkat lunak gratis. Perpustakaan menggunakan implementasi sistem untuk berinteraksi dengan antarmuka dan menyediakan kelas untuk operasi parsing, menghubungkan, membaca, dan menulis menggunakan port serial. Lebih lanjut tentang perpustakaan ini dapat ditemukan di sini .

Pustaka Swing bawaan yang lama namun andal digunakan sebagai alat untuk mengembangkan antarmuka pengguna. Karena kemampuan untuk mengubah tema, UI sederhana di Swing mungkin tidak terlihat

Program itu sendiri sangat sederhana dan terutama menggunakan kemampuan terdokumentasi dari pustaka RTXT.

Fungsionalitas utama program

Beginilah cara menentukan port yang tersedia:

public String[] getPorts() {

ports = CommPortIdentifier.getPortIdentifiers();

while (ports.hasMoreElements()) {

CommPortIdentifier curPort = (CommPortIdentifier) ports.nextElement();

if (curPort.getPortType() == CommPortIdentifier.PORT_SERIAL) {

portMap.put(curPort.getName(), curPort);

}

}

return portMap.keySet().toArray(new String[0]);

}

Menghubungkan ke port yang dipilih:

public void connect() {

String selectedPort = (String)gui.ports.getSelectedItem();

selectedPortIdentifier = portMap.get(selectedPort);

CommPort commPort;

try{

commPort = selectedPortIdentifier.open("UART controller", TIMEOUT);

serialPort = (SerialPort)commPort;

serialPort.setSerialPortParams(BAUD_RATE, SerialPort.DATABITS_8, SerialPort.STOPBITS_1, SerialPort.PARITY_NONE);

gui.writeLog(selectedPort + " opened successfully.");

}catch (PortInUseException e){

gui.writeLogWithWarning(selectedPort + " is in use. (" + e.toString() + ")");

}catch (Exception e){

gui.writeLogWithWarning("Failed to open " + selectedPort + " (" + e.toString() + ")");

}

}

Proses transfer data:

public boolean writeData(byte[] bytes){

boolean successfull = false;

try {

gui.writeLog("WRITING: " + HexBinUtil.stringFromByteArray(bytes));

output.write(bytes);

output.flush();

successfull = true;

}

catch (Exception e) {

gui.writeLogWithWarning("Failed to write data. (" + e.toString() + ")");

}

return successfull;

}

Menerima data:

public void serialEvent(SerialPortEvent serialPortEvent) {

if (serialPortEvent.getEventType() == SerialPortEvent.DATA_AVAILABLE) {

try {

byte singleData = (byte)input.read();

gui.writeLog("READING: " + HexBinUtil.stringFromByteArray(singleData));

}

catch (Exception e) {

gui.writeLogWithWarning("Failed to read data. (" + e.toString() + ")");

}

}

}

Seperti yang telah disebutkan, DAC / ADC dikontrol dengan mengirimkan perintah untuk menulis beberapa nilai 8-bit yang valid ke alamat register tertentu yang dijelaskan dalam dokumentasi. Untuk menentukan status register saat ini, Anda harus mengirim perintah baca dan menentukan alamat register yang diminta. Deskripsi lengkap seperti biasa di dokumentasi .

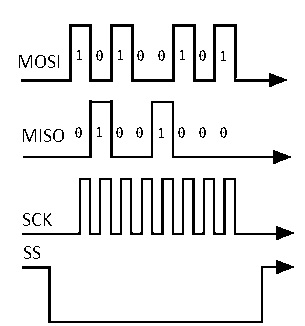

Transmisi data UART

Dalam proses mempelajari AD9993-EBZ, ditemukan bahwa hanya 8 bit data yang digunakan dalam ruang alamat register 12-bit yang tersedia. Juga, nilai yang dikirimkan dari status register dijelaskan oleh 8 bit. Untuk menentukan jenis transfer data (tulis / baca), diperlukan transfer 1 bit data.

Karena batasan saat ini pada ukuran maksimum pesan melalui antarmuka UART adalah 8 bit data, maka diputuskan untuk mengirimkan 3 pesan 8-bit berturut-turut selama proses penulisan dan 2 pesan selama proses pembacaan.

Paket pertama akan berisi jenis transmisi data, digandakan untuk seluruh ukuran paket. Oleh karena itu, hanya ada dua kemungkinan nilai: 00000000 untuk membaca dan 11111111 untuk menulis. Penggunaan ledakan integer untuk transmisi satu bit data dilakukan untuk menyederhanakan pemrosesan lebih lanjut dari sinyal yang diterima.

Selanjutnya, alamat register yang diminta dan nilai status register yang ditransmisikan selama proses perekaman ditransmisikan.

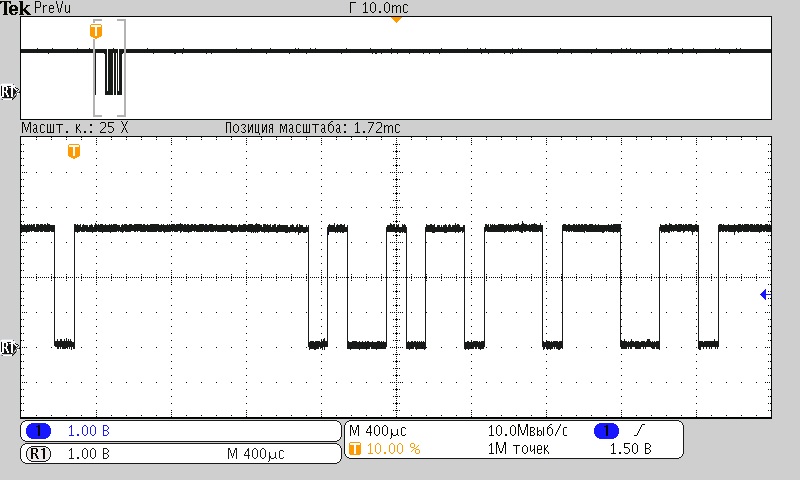

Osilogram dari paket UART yang dikembangkan

Antarmuka pengguna

Elemen utama dari antarmuka pengguna perangkat lunak adalah tombol untuk menghubungkan / memutuskan sambungan dari port serial yang tersedia (elemen 3,4), bidang untuk memasukkan alamat dan nilai register (elemen 7,8), jendela log (elemen 6). Perangkat lunak ini dirancang untuk berinteraksi dengannya dalam dua kondisi: "terhubung ke port" dan "terputus dari port". Status menentukan aktivitas beberapa elemen pada antarmuka program, dan juga membatasi eksekusi metode tertentu untuk mengurangi kemungkinan kesalahan dan penggunaan perangkat lunak yang salah. Saat diaktifkan, program berada dalam status "terputus dari port". Juga, untuk memfasilitasi kerja dengan program (yang saya adalah salah satu tujuan utama proyek), fungsi menghubungkan file dengan perintah yang sudah disimpan dalam format JSON ditambahkan (elemen 10).

Proses pemuatan perintah:

Pemilihan file

Antarmuka perintah

Fungsionalitas memungkinkan Anda untuk mengurutkan perintah yang dimuat menjadi beberapa bagian (elemen 12), menyesuaikan proses bekerja dengan perintah yang terhubung (apakah akan mengirim perintah ke port serial segera saat ditekan, atau mengisi kolom alamat dan nilai sesuai dengan perintah yang dipilih) ...

Pengembangan proyek untuk FPGA

informasi Umum

Sebelum Anda mulai mengembangkan proyek untuk FPGA, Anda perlu memutuskan tugas yang harus dia selesaikan.

Kedengarannya seperti ini: proyek untuk FPGA harus mendukung konversi data berikut:

Diagram konversi data

DE10-Nano menerima sinyal dari garis Tx antarmuka UART (sinyal atas). Selanjutnya, FPGA perlu menentukan dengan benar data yang diterima dari tiga pesan masing-masing 8 bit dan mengubahnya menjadi format pesan SPI yang sesuai dengan dokumentasi (disajikan dalam 4 baris).

Modul utama yang diperlukan untuk mengimplementasikan konversi ini adalah modul pengontrol UART dan modul pengontrol SPI. Kepada merekalah sisa bab ini ditugaskan.

Saat mengembangkan proyek untuk FPGA, digunakan IDE Qartus Prime Lite Edition versi 17.

Jika Anda tidak memiliki pengalaman menggunakan Quartus atau belum memprogram FPGA sama sekali, disarankan untuk memulai dengan contoh yang jelas (menurut saya) dari proyek pertama di Quartus.

Saya ingin mencatat bahwa semua ekstrak dari kode Verilog yang dijelaskan di bawah ini adalah kompilasi solusi yang ditemukan di Internet, yang tidak berpura-pura menjadi orisinalitas apa pun. Sekali lagi, tujuan utama proyek ini adalah untuk menyelesaikan masalah tertentu.

Pengontrol UART

Deskripsi

Pengontrol UART terdiri dari tiga modul:

- generator pulsa;

- modul perekaman;

- modul membaca.

Dianjurkan untuk melihat artikel ini , dari mana sebagian besar informasi diambil. Selanjutnya, saya hanya akan fokus pada detail implementasi yang paling penting (menurut saya).

Generator pulsa

Karena antarmuka UART tidak sinkron, penerima perlu menghasilkan sinyal referensi sendiri untuk menerima sinyal yang ditransmisikan dengan benar, yang memungkinkannya menentukan awal bit informasi baru dengan benar.

Ada kisaran standar baud rate UART yang diterima secara umum: 300; 600; 1200; 2400; 4800; 9600; 19200; 38400; 57600; 115200; 230400; 460800; 921600 baud Dalam kasus kami, transfer data terjadi pada 9600 baud. Selanjutnya kita perlu mendapatkan generator dengan frekuensi 16 kali simbol rate. Ini diperlukan untuk mendeteksi dengan benar level sinyal yang dikirim.

Untuk menghasilkan pulsa, generator 50 MHz digunakan pada chip. Untuk mendapatkan frekuensi yang diinginkan, perlu memperhitungkan setiap 325 pulsa generator.

Beginilah tampilannya di Verilog:

input Clk; // 50

input Rst_n; //

input [15:0] BaudRate; // , 325

output Tick; //

reg [15:0] baudRateReg; //

always @(posedge Clk or negedge Rst_n)

if (!Rst_n) baudRateReg <= 16'b1;

else if (Tick) baudRateReg <= 16'b1;

else baudRateReg <= baudRateReg + 1'b1;

assign Tick = (baudRateReg == BaudRate);

endmodule

Modul pembaca

Pembaca mengubah sinyal input dari garis RX menjadi array data 8-bit output.

Langsung membaca dan mentransfer data yang telah dibaca ke output:

input Clk, Rx,Tick; // 50, Rx,

input [3:0]NBits; // , 8

output RxDone; //

output [7:0]RxData; //

reg read_enable = 1'b0; //

reg RxDone = 1'b0; //

reg [3:0] counter = 4'b0000; //

reg start_bit = 1'b1; //

reg [4:0]Bit = 5'b00000; //

reg [7:0] RxData; //

reg [7:0] Read_data= 8'b00000000; //

always @ (posedge Tick) //

begin

if (read_enable)

begin

RxDone <= 1'b0; //

counter <= counter+1'b1; //

if ((counter == 4'b1000) & (start_bit)) //

begin

start_bit <= 1'b0;

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (!start_bit) & (Bit < NBits)) //

begin

Bit <= Bit+1'b1;

Read_data <= {Rx,Read_data[7:1]};

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (Bit == NBits) & (Rx)) //

begin

Bit <= 4'b0000;

RxDone <= 1'b1; //

counter <= 4'b0000; //

start_bit <= 1'b1; //

end

end

end

always @ (posedge Clk)

begin

if (NBits == 4'b1000) // 8 ,

begin

RxData[7:0] <= Read_data[7:0];

end

end

Modul transmisi

Modul transmisi mengubah sinyal input 8-bit menjadi paket data serial UART.

Transfer data langsung:

input Clk, Rst_n, TxEn; // 50, ,

input Tick; //

input [3:0]NBits; //

input [7:0]TxData;

output Tx;

output TxDone;

reg Tx;

reg TxDone = 1'b0;

reg write_enable = 1'b0;

reg start_bit = 1'b1;

reg stop_bit = 1'b0;

reg [4:0] Bit = 5'b00000;

reg [3:0] counter = 4'b0000;

reg [7:0] in_data=8'b00000000;

always @ (posedge Tick) //

begin

if (!write_enable)

begin

TxDone = 1'b0;

start_bit <=1'b1;

stop_bit <= 1'b0;

end

if (write_enable)

begin

counter <= counter+1'b1; //

if(start_bit & !stop_bit)//

begin

Tx <=1'b0;

in_data <= TxData;

if ((counter == 4'b1111) & (start_bit) ) //

begin

start_bit <= 1'b0;

in_data <= {1'b0,in_data[7:1]};

Tx <= in_data[0];

end

if ((counter == 4'b1111) & (!start_bit) & (Bit < NBits-1)) //

begin

in_data <= {1'b0,in_data[7:1]};

Bit<=Bit+1'b1;

Tx <= in_data[0];

start_bit <= 1'b0;

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (Bit == NBits-1) & (!stop_bit)) //

begin

Tx <= 1'b1;

counter <= 4'b0000;

stop_bit<=1'b1;

end

if ((counter == 4'b1111) & (Bit == NBits-1) & (stop_bit) ) //

begin

Bit <= 4'b0000;

TxDone <= 1'b1;

counter <= 4'b0000;

//start_bit <=1'b1;

end

end

end

Pengontrol SPI

Penyimpangan penting

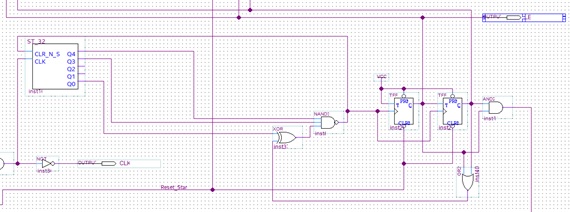

Karena pengontrol SPI, yang diimplementasikan atas dasar FPGA, adalah struktur logis yang lebih kompleks daripada pengontrol UART, penjelasan lebih lanjut tentang logika operasi lebih mudah dilakukan pada model rangkaian pengontrol.

Skema umum pengontrol

Model yang dikembangkan dapat dibagi menjadi 3 modul utama:

- modul tulis berurutan;

- modul penghitung bit;

- modul penganalisis kesalahan.

Pembagian menjadi modul agak sewenang-wenang, karena rangkaian memiliki konektivitas tinggi antar elemen yang digunakan. Pembagian didasarkan pada tugas-tugas yang dilakukan oleh masing-masing kelompok elemen yang disajikan dalam diagram umum.

Clocking sirkuit disediakan oleh sinyal 12,5 MHz yang disuplai melalui saluran CLK_125.

Awal pekerjaan pengontrol pada pembentukan pesan kontrol dilakukan oleh sinyal "MULAI". Dengan sinyal ini, semua modul rangkaian diatur ke keadaan awalnya dan awal siklus menghasilkan sinyal yang diperlukan pada jalur keluaran CLK, SS, MOSI dari antarmuka SPI diinisialisasi

Modul tulis berurutan

Modul serial write akan menjalankan tugas utama dari pengontrol SPI, yaitu mengeluarkan data bit paralel ke jalur serial MOSI. Ini karena elemen RG_24_PI_SO, yang beroperasi berdasarkan prinsip register geser berdasarkan D-flip-flop.

Elemen RG_24_PI_SO memiliki 24 input data yang sesuai dengan dokumentasi AD9993-EBZ pada format pengiriman SPI. Mereka termasuk:

- Data perintah (DATA_0 - DATA_7);

- Daftarkan data alamat (ADR_0 - ADR_12);

- Bit mode tulis / baca W / R.

Sinyal yang disajikan ditulis secara paralel pada level logika "1" pada input LoadP_ShiftN. Selanjutnya, pada level logika "0" pada input LoadP_ShiftN, pada setiap siklus clock pada input CLK, elemen tersebut secara bergantian mereproduksi data yang direkam ke jalur serial dari output MOSI.

Modul penghitung bit

Modul penghitung bit diperlukan untuk menentukan durasi sinyal pengaktifan penulisan data pada garis SS antarmuka SPI. Karena, menurut dokumentasi AD9993-EBZ, durasi sinyal pengaktifan harus sama dengan durasi total data yang ditransmisikan, maka diperlukan penghitungan 24 pulsa sinkronisasi dari awal transmisi data untuk menentukan durasi yang diperlukan dari sinyal pengaktifan. Fungsi penghitungan dilakukan oleh elemen ST_32, yang, ketika sinyal clock ke-24 terdeteksi, mereproduksi sinyal yang digunakan untuk mengatur ulang penghitung dan juga untuk mengakhiri sinyal pengaktifan yang ditransmisikan.

Selain fungsi utama, modul penghitung bit juga bertanggung jawab untuk menginisialisasi proses analisis kesalahan, tindakan awalnya adalah mengirim perintah nilai baca ke alamat register yang terakhir direkam. Karena proses analisis kesalahan harus dimulai setelah interval waktu yang setara dengan durasi 23 pulsa sinkronisasi sejak bit data terakhir yang ditransmisikan dikirim (dibuat secara eksperimental), penghitung bit setelah sinyal reset beralih ke mode penghitungan pulsa sinkron 23, yang memastikan pengoperasian proses analisis kesalahan.

Modul analisis kesalahan

Seperti yang disebutkan dalam penjelasan modul sebelumnya, untuk menyediakan fungsionalitas analisis kesalahan, dikembangkan metode berdasarkan pembacaan nilai perintah yang disimpan pada IC di alamat register yang digunakan dalam proses pencatatan data. Proses membaca diperlukan untuk membandingkan nilai tertulis dengan data yang dibaca untuk mengidentifikasi inkonsistensi, dan oleh karena itu untuk menentukan kesalahan yang telah terjadi. Modul analisis kesalahan didasarkan pada elemen RG_8_SI_PO, yang beroperasi berdasarkan prinsip register geser. Elemen mengubah sinyal yang diterima melalui port serial MISO menjadi output 8-bit paralel. Kemudian data tersebut dibandingkan dengan nilai perintah yang digunakan selama proses perekaman data. Fungsionalitas perbandingan dilakukan oleh elemen CMP_8 berdasarkan eksklusif-atau logika. Jika ditemukan perbedaan,modul mengirimkan sinyal ke output LED, yang akan berada dalam status unit logis hingga proses perekaman data berikutnya. Diasumsikan bahwa output LED akan dihubungkan ke salah satu LED, sekelompok yang ada di papan pengembangan Nano DE10, yang secara visual akan menandakan kesalahan yang telah terjadi.

Kesimpulan

Sebagai hasil dari pemecahan masalah ini, skema interaksi antara PC dan perangkat DAC / ADC dirancang dan diimplementasikan secara fisik dengan sejumlah keunggulan utama. Dalam proses implementasi, masalah dengan koneksi FPGA dan PC terpecahkan. Solusi untuk ini adalah dengan menggunakan modul UART eksternal. Perangkat lunak PC ditulis dalam Java. Perangkat lunak ini memiliki antarmuka dengan kemampuan dasar untuk mengirim dan menerima data dalam format pengiriman UART yang dikembangkan, selain itu, memiliki fungsi memuat perintah yang disimpan. Kontroler UART dan SPI berbasis FPGA dikembangkan.

Masalah-masalah yang dipertimbangkan dalam kerangka proyek ini memungkinkan:

- mengevaluasi cara interaksi sirkuit terintegrasi dengan perangkat eksternal;

- mengevaluasi cara menggunakan FPGA sebagai perangkat yang cocok, buffer untuk pertukaran data;

- mengeksplorasi salah satu pendekatan paling efektif untuk mengembangkan perangkat lunak untuk penggunaan praktis.

PS Saya akan senang dengan penambahan, komentar dan indikasi kesalahan.