IBM mengumumkan pengembangan teknologi proses 2nm.

Apa yang diumumkan:

- 2 nm.

- 50 miliar transistor dalam satu area seukuran paku. Kemudian mereka mengklarifikasi - pada area seluas 150 mm persegi - yaitu, 333 juta transistor per milimeter persegi (

- MTx / mm 2 ).

- Pitch gerbang transistor (Contacted Poly Pitch, CPP) adalah 44 nm, panjang gerbang adalah 12 nm.

- (Gate All Around, GAA). – , IBM (horizontal nanosheets, HNS).

- HNS .

- 45% 75% 7 .

- (EUV) HNS 15 70 . , SRAM.

- 5 .

Apakah ini benar-benar teknologi proses 2nm? Saat ini TSMC adalah pemimpin dalam produksi chip. Kami memplot hubungan antara nama proses TSMC dan kerapatan transistor dengan mendekati kurva dengan koefisien determinasi 0,99.

Dari 28nm hingga 5nm, angka aktual digunakan menurut IC Knowledge dan TechInsights. Angka 3nm didasarkan pada siaran pers TSMC. 2 nm dan 1,5 nm adalah ekstrapolasi kami.

Dengan menggunakan grafik, Anda dapat mengubah kerapatan transistor menjadi teknologi proses TSMC yang setara (TSMC Equivalent Node, atau TEN). Kami mendapatkan 2,9 nm untuk 333 MTx / mm 2 . Dari sudut pandang kami, ternyata ini adalah teknologi proses 3 nm, bukan 2 nm.

Untuk membandingkan secara lebih detail antara pengumuman dari IBM dengan pengumuman sebelumnya tentang teknologi proses 3nm dan proses 2nm yang diusulkan, beberapa asumsi perlu dibuat.

- Diketahui dari pengumuman bahwa CPP adalah 44 nm.

- Misalkan produksi menggunakan teknologi penempatan transistor paling ketat, Single Diffusion Break (SDB).

- Berdasarkan foto cutaway dari pengumuman tersebut, teknologi Buried Power Rails (BPR) tidak digunakan. BPR diperlukan untuk mengurangi ukuran track HNS menjadi 5.0 - jadi anggaplah nilai ini 6.0 dalam proses ini.

- Untuk mencapai kerapatan 333 MTx / mm 2 , Jarak Logam Minimum harus 18 nm - nilai yang sangat agresif yang mungkin memerlukan fotolitografi multi-matriks EUV.

2nm IBM versus teknologi proses 3nm yang ada

Tabel berikut membandingkan desain IBM dengan perkiraan proses 3nm kami dari Samsung dan TSMC. Kami tahu Samsung juga bekerja dengan HNS, dan TSMC telah menetapkan FinFET 3nm. Samsung dan TSMC juga mengumumkan peningkatan kepadatan transistor 3nm untuk teknologi proses mereka dibandingkan dengan 5nm. Oleh karena itu, kerapatan transistor dari ketiga perusahaan diketahui oleh kami, dan kami dapat menghitung SEPULUH untuk semua. TEN IBM adalah 2,9; terlihat bahwa Samsung memiliki 4.7, dan TSMC memiliki 3.0. Sekali lagi, ternyata 2 nm dari IBM lebih mirip dengan 3 nm dari TSMC, sedangkan Samsung tertinggal.

Parameter indikatif yang diperlukan untuk mencapai kepadatan yang diumumkan disorot dengan warna merah, dengan asumsi semua perusahaan menggunakan teknologi SDB. Ketinggian track paling kecil di TSMC, karena tanpa BPR di FinFET parameter ini bisa mencapai 5.0, namun agar HNS memiliki tinggi yang sama, BPR harus digunakan.

2nm IBM versus teknologi proses 2nm yang ada

Pada tabel berikut, kami memperkirakan nilai parameter untuk teknologi proses 2 nm dari Samsung dan TSMC. Dalam ekstrapolasi kami, kami berasumsi bahwa perusahaan menggunakan BPR (teknologi BPR belum matang, tetapi kemungkinan akan beroperasi saat mereka mengumumkan proses 2nm pada tahun 2023-2024). Mari kita asumsikan juga bahwa perusahaan mengadopsi arsitektur lembar garpu NHS (HNS FS) untuk mencapai ketinggian lintasan 4,33. Perkiraan CPP dan MPP didasarkan pada tren terkini dalam miniaturisasi teknologi.

Konsumsi daya dan kinerja

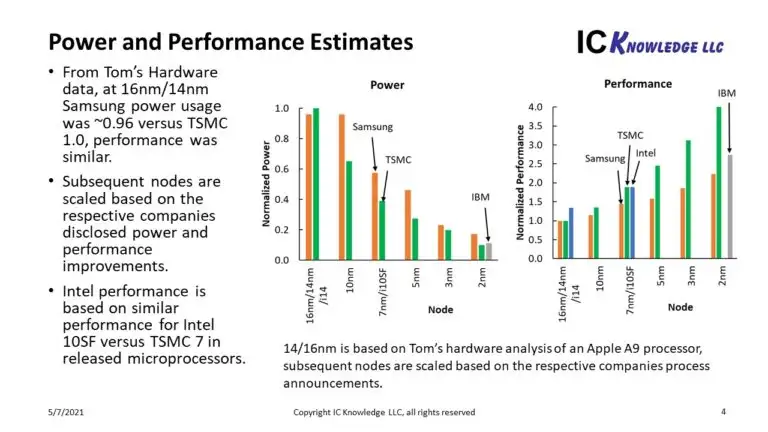

Tahun ini saya sudah membuat tebakan tentang konsumsi daya dan kinerja perangkat dari Samsung dan TSMC menggunakan data kinerja tambahan dari Intel. Ekstrapolasi didasarkan pada jaminan dari perusahaan dan perbandingan dunia nyata antara proses 14nm dan 16nm.

Karena IBM telah membandingkan peningkatan dalam konsumsi daya dan kinerja dengan proses manufaktur 7nm tingkat lanjut, saya dapat memplot data mereka pada grafik yang sama.

Melalui penggunaan HNS, IBM telah melihat penghematan daya yang signifikan, membuat proses 2nm mereka lebih efisien daripada proses 3nm dari Samsung dan TSMC. Meskipun menurut kami, ketika TSMC beralih ke HNS pada 2 nm, konsumsi dayanya tidak akan kalah dengan IBM. Dalam hal kinerja, kami berasumsi bahwa proses 3nm TSMC akan melebihi proses 2nm IBM.

Tentu saja, ini semua hanyalah perkiraan berdasarkan sejumlah besar asumsi.

Kesimpulan

Setelah menganalisis pengumuman IBM, kami sampai pada kesimpulan bahwa teknologi proses 2 nm mereka lebih mirip dengan teknologi proses 3 nm dari TSMC dalam hal kepadatan transistor, sementara memiliki indikator konsumsi daya terbaik, tetapi lebih rendah dalam kecepatan. Pernyataan dari IBM sangat mengesankan - namun, ini hanyalah sampel laboratorium, yang jelas melampaui 3 nm dari TSMC hanya dalam hal konsumsi daya. Pada saat yang sama, kumpulan berisiko pertama dari perangkat 3 nm dari TSMC akan muncul tahun ini, dan yang komersial tahun depan.

Menurut kami, TSMC akan mempertahankan keunggulan dalam kepadatan, konsumsi daya, dan kecepatan perangkat berdasarkan teknologi proses 2nm saat mulai diproduksi pada 2023-2024.