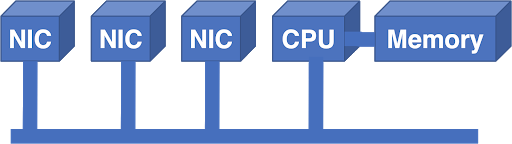

Pada masa-masa awal, router adalah komputer biasa dengan Network Interface Cards (NIC) yang terpasang pada bus.

Gambar 1 - Kartu antarmuka jaringan yang terhubung ke bus.

Sampai titik tertentu, sistem seperti itu berhasil. Dalam arsitektur ini, paket memasuki NIC dan dipindahkan dari NIC ke memori oleh CPU. CPU membuat keputusan penerusan dan mengeluarkan paket ke NIC eksternal. CPU dan memori adalah sumber daya terpusat dengan dukungan perangkat terbatas. Bus juga merupakan batasan tambahan: bandwidth bus harus mendukung bandwidth semua NIC pada waktu yang sama.

Jika jaringan perlu ditingkatkan, masalah mulai muncul dengan sangat cepat. Anda dapat membeli prosesor yang lebih cepat, tetapi bagaimana cara meningkatkan daya bus? Jika Anda menggandakan kecepatan bus, Anda perlu menggandakan kecepatan antarmuka bus pada setiap NIC dan CPU. Ini meningkatkan biaya semua papan, bahkan jika kapasitas satu NIC tidak meningkat.

Pelajaran satu: biaya router harus tumbuh secara linier dengan kemampuannya

Terlepas dari pelajaran yang didapat, solusi yang mudah untuk meningkatkan skala adalah dengan menambahkan bus dan prosesor lain:

Gambar 2 - Solusi untuk masalah penskalaan sistem adalah dengan menambahkan bus dan prosesor baru.

Arithmetic Logic Unit (ALU) adalah chip Digital Signal Processing (DSP) yang dipilih karena rasio harga-kinerja yang superior. Bus tambahan meningkatkan bandwidth, tetapi arsitekturnya tidak tumbuh dalam skalanya. Dengan kata lain, lebih banyak ALU dan bus tidak dapat ditambahkan untuk meningkatkan produktivitas.

Karena ALU masih merupakan batasan yang signifikan, langkah selanjutnya adalah menambahkan Field Programmable Gate Array (FPGA) ke arsitektur untuk mengurangi beban pencarian Longest Prefix Match (LPM).

Gambar 3 - Langkah selanjutnya adalah menambahkan Field Programmable Gate Array.

Meskipun ini membantu, itu tidak sepenuhnya menyelesaikan masalah. ALU masih kewalahan. LPM membuat sebagian besar beban, tetapi arsitektur terpusat masih tidak berskala dengan baik, bahkan jika kami menyingkirkan beberapa masalah.

Pelajaran dua: LPM dapat diimplementasikan dalam silikon dan bukan merupakan penghalang kinerja

Terlepas dari pelajaran ini, langkah selanjutnya diambil ke arah yang berbeda: mengganti ALU dan FPGA dengan prosesor standar. Para desainer mencoba untuk meningkatkan dengan menambahkan lebih banyak CPU dan lebih banyak bus. Butuh banyak upaya bahkan untuk peningkatan daya yang kecil, dan sistem masih mengalami keterbatasan bandwidth dari bus terpusat.

Pada tahap evolusi Internet ini, kekuatan yang lebih serius mulai bekerja. Ketika web menjadi populer di kalangan masyarakat umum, potensi Internet mulai menjadi lebih nyata. Telcos memperoleh jaringan NSFnet regional dan mulai membangun kompleks komersial. Sirkuit Terpadu Khusus Aplikasi (ASIC) telah menjadi teknologi yang terbukti, memungkinkan lebih banyak fungsionalitas untuk diterapkan secara langsung dalam silikon. Permintaan untuk router telah meroket, dan kebutuhan untuk peningkatan skalabilitas yang signifikan akhirnya mengalahkan konservatisme teknik. Untuk memenuhi permintaan ini, banyak startup bermunculan dengan berbagai solusi yang memungkinkan.

Palang yang terjadwal menjadi salah satu alternatif:

Gambar 4 - Palang terjadwal.

Dalam arsitektur ini, setiap NIC memiliki masukan dan keluaran. Prosesor NIC membuat keputusan penerusan, memilih NIC keluaran, dan mengirim permintaan penjadwalan ke sakelar (palang). Penjadwal menerima semua permintaan dari NIC, mengerjakan solusi optimal, memprogram solusi ke dalam sakelar, dan mengarahkan input untuk transmisi.

Masalah dengan skema ini adalah bahwa setiap keluaran dapat "mendengarkan" satu masukan pada satu waktu, dan lalu lintas Internet berdenyut. Jika dua paket perlu mencapai pintu keluar yang sama, salah satunya harus menunggu. Menunggu satu paket menyebabkan paket lain menunggu pada input yang sama, setelah itu sistem mulai mengalami Pemblokiran Head Of Line (HOLB), yang mengakibatkan kinerja router yang sangat buruk.

Pelajaran tiga: struktur internal router tidak boleh memblokir sinyal bahkan dalam kondisi beban

Migrasi ke chip khusus juga memotivasi perancang untuk bermigrasi ke struktur berbasis sel internal, karena mengganti sel berukuran tetap kecil jauh lebih mudah daripada berurusan dengan paket dengan panjang variabel, yang terkadang berukuran besar. Namun, penggunaan sel switching juga berarti bahwa penjadwal harus berjalan pada frekuensi yang lebih tinggi, membuat penjadwalan jauh lebih sulit.

Pendekatan inovatif lainnya adalah membangun NIC menjadi torus:

Gambar 5 - NIC berbentuk torus.

Dalam skema seperti itu, setiap NIC memiliki koneksi ke empat tetangga, dan NIC masukan harus menghitung jalur melalui struktur untuk mencapai kartu jalur keluaran. Sistem ini mengalami masalah - bandwidth tidak sama. Lebar transmisi pada arah utara-selatan lebih tinggi dibandingkan pada arah timur-barat. Jika pola lalu lintas masuk bergerak timur-barat, kemacetan akan terjadi.

Pelajaran empat: struktur internal router harus memiliki distribusi bandwidth yang merata, karena kita tidak dapat memprediksi distribusi lalu lintas.

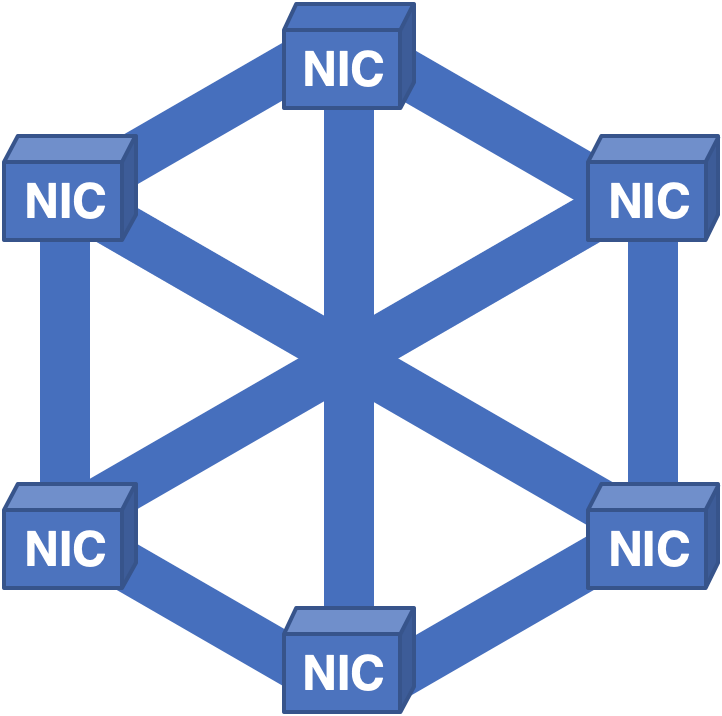

Pendekatan yang sama sekali berbeda adalah membuat jaringan komunikasi NIC-NIC lengkap dan mendistribusikan sel ke semua NIC:

Gambar 6 - Struktur yang terhubung sepenuhnya dengan distribusi sel ke semua NIC.

Meskipun mempelajari pelajaran sebelumnya, masalah baru teridentifikasi. Dalam arsitektur ini, semuanya bekerja dengan cukup baik sampai perlu melepas papan untuk diperbaiki. Karena setiap NIC berisi sel untuk semua paket dalam sistem, saat kartu dihapus, tidak ada paket yang dapat dibuat ulang, mengakibatkan waktu henti yang singkat namun menyakitkan.

Pelajaran Lima: Router Seharusnya Tidak Memiliki Satu Titik Kegagalan

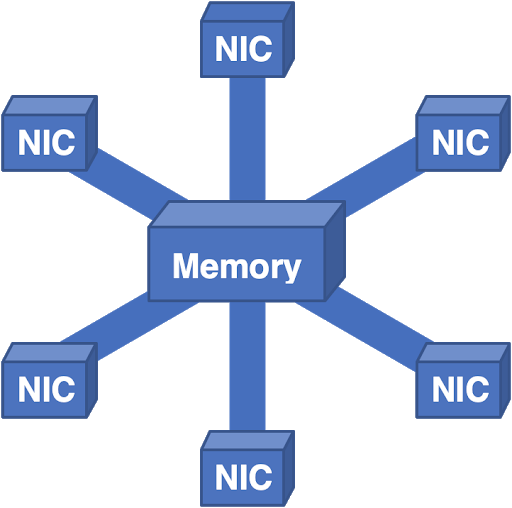

Kami bahkan mengambil arsitektur ini dan membaliknya:

Gambar 7 - Di sini semua paket pergi ke memori pusat dan kemudian ke NIC keluar.

Sistem ini bekerja dengan cukup baik, tetapi penskalaan memori menjadi masalah. Anda bisa menambahkan beberapa pengontrol dan bank memori, tetapi pada titik tertentu keseluruhan bandwidth menjadi terlalu rumit untuk desain fisik. Dihadapkan pada kendala fisik praktis, kami dipaksa untuk berpikir ke arah lain.

Jaringan telepon telah menjadi sumber inspirasi bagi kami. Dahulu kala, Charles Close menyadari bahwa sakelar yang dapat diskalakan dapat dibuat dengan membangun jaringan sakelar yang lebih kecil. Ternyata, semua properti luar biasa yang kami butuhkan ada di jaringan Clos:

Gambar 8 - Jaringan Clos.

Tutup properti jaringan:

- Kekuatan tumbuh dengan skala.

- Tidak memiliki satu pun titik kegagalan.

- Mempertahankan redundansi yang cukup untuk toleransi kesalahan.

- Mengatasi kelebihan beban dengan mendistribusikan beban ke seluruh struktur.

Kami selalu mengimplementasikan input dan output secara bersamaan, jadi kami biasanya melipat gambar ini di sepanjang garis putus-putus. Ini menghasilkan jaringan Clos terlipat, dan inilah yang kami gunakan hari ini di router multi-case: beberapa kasus memiliki NIC dan lapisan sakelar, di lain-lain - lapisan sakelar tambahan.

Gambar 9 - Jaringan Clos yang Runtuh.

Sayangnya, arsitektur inipun memiliki masalah tersendiri. Format sel yang digunakan di antara sakelar adalah milik dan dimiliki oleh produsen chip, yang mengarah pada ketergantungan pada chipset. Ketergantungan pada vendor chip tidak jauh lebih baik daripada ketergantungan pada vendor router tunggal, masalahnya sama: mengikat harga dan ketersediaan perangkat ke satu sumber. Peningkatan perangkat keras menantang karena sakelar sel baru harus secara bersamaan mendukung koneksi lama dan format sel untuk menjaga interoperabilitas, serta semua kecepatan tautan dan format sel peralatan baru.

Setiap sel harus dialamatkan untuk menunjukkan NIC jalan keluar yang harus dikirimi informasi. Pengalamatan seperti itu terbatas, yang menciptakan batas skalabilitas. Kontrol dan manajemen di router multi-kasus masih sepenuhnya eksklusif, menyebabkan masalah vendor tunggal lainnya dalam tumpukan perangkat lunak.

Untungnya, kami dapat menyelesaikan masalah ini dengan mengubah filosofi arsitektur kami. Selama lima puluh tahun terakhir, kami telah berupaya untuk menskalakan router. Kami telah belajar dari pengalaman membangun awan besar bahwa filosofi skala keluar seringkali lebih berhasil.

Arsitektur scale-out menggunakan strategi divide and conquer daripada membuat server tunggal yang besar dan sangat cepat. Rak server kecil dapat melakukan pekerjaan yang sama sekaligus lebih andal, fleksibel, dan hemat biaya.

Pendekatan ini juga berlaku untuk router. Apakah mungkin untuk mengambil beberapa router kecil dan mengaturnya dalam topologi Clos untuk mencapai manfaat arsitektur yang serupa sambil menghindari masalah terkait mesh? Ternyata, ini tidak terlalu sulit:

Gambar 10 - Mengganti sakelar sel dengan sakelar paket, mempertahankan topologi Clos untuk penskalaan yang lebih mudah.

Dengan mengganti sakelar sel dengan sakelar paket dan mempertahankan topologi Clos, kami memberikan kemudahan skalabilitas.

Penskalaan dapat dilakukan dalam dua dimensi: menambahkan router masuk baru dan sakelar paket secara paralel dengan lapisan yang ada, atau menambahkan lapisan sakelar tambahan. Karena router individu cukup terstandarisasi saat ini, kami menghindari ketergantungan pada satu vendor. Semua tautan menggunakan Ethernet standar, jadi tidak ada masalah kompatibilitas.

Peningkatan dapat dilakukan dengan mudah dan langsung: jika sakelar membutuhkan lebih banyak saluran, Anda dapat menggantinya dengan sakelar yang lebih besar. Jika Anda perlu meningkatkan saluran terpisah dan kedua ujung saluran memiliki kemampuan ini, maka Anda hanya perlu meningkatkan optik. Kecepatan transmisi yang berbeda dari link yang berbeda dalam suatu fabric tidak menjadi masalah karena setiap router bertindak sebagai pemeta kecepatan.

Arsitektur ini sudah populer di dunia pusat data dan, tergantung pada jumlah lapisan sakelar, disebut arsitektur leaf-spine atau super-spine. Ini telah terbukti sangat andal, stabil dan fleksibel.

Dari sudut pandang bidang transmisi, jelas bahwa ini adalah alternatif arsitektur yang layak. Masalah tetap ada pada bidang kendali dan bidang kendali. Menskalakan bidang kontrol memerlukan urutan peningkatan skala dalam skala protokol kontrol kami. Kami mencoba menerapkannya dengan meningkatkan mekanisme abstraksi dengan membuat representasi proxy dari arsitektur yang menggambarkan seluruh topologi sebagai satu node.

Demikian juga, kami sedang bekerja untuk mengembangkan abstraksi bidang kontrol yang akan memungkinkan kami untuk mengontrol seluruh struktur Clos sebagai satu router. Pekerjaan ini dilakukan sebagai standar terbuka, jadi tidak ada teknologi yang terlibat yang merupakan hak milik.

Selama lima puluh tahun, arsitektur router telah berkembang pesat, dan banyak kesalahan telah dibuat dalam proses menemukan trade-off antara teknologi yang berbeda. Jelas sekali, evolusi kita belumlah sempurna. Dalam setiap iterasi, kami menangani masalah generasi sebelumnya dan menemukan tantangan baru.

Mudah-mudahan, dengan mempelajari pengalaman masa lalu dan saat ini secara saksama, kami dapat bergerak maju menuju arsitektur yang lebih fleksibel dan andal serta membuat perbaikan di masa mendatang tanpa sepenuhnya mengganti perangkat keras.