Saya sudah berbicara tentang pengantin baru Vladislav dan Elena Sharshin, yang, bersama dengan rekan mereka Andrey Papushin, membawa Intel ke California untuk meraih kemenangan perak dalam kompetisi InnovateFPGA. Wawancara mereka dilakukan di lab "Digital Synthesis" yang baru-baru ini diterbitkan . Labnik ini akan kami gunakan pada seminar untuk anak sekolah dan siswa SMP, yang akan berlangsung pada tanggal 15-17 September di pameran ChipEXPO di Skolkovo . Jika Anda akan mengulangi (atau melampaui) pencapaian Sharshin dan Papushin, atau hanya menjadi seorang desainer FPGA atau ASIC tanpa meninggalkan Santa Clara, maka berpartisipasi dalam seminar, atau bahkan hanya melihat petunjuk awal di posting ini, akan membantu Anda memulai.

Banyak dari mereka yang mendaftar untuk seminar ini telah mendapatkan papan FPGA (didistribusikan oleh departemen pendidikan RUSNANO) karena telah lulus prasyarat teori . Sekarang akan sangat diinginkan jika peserta seminar menginstal Intel FPGA Quartus (atau, jika seseorang tidak menyukai Intel / Altera, maka Xilinx Vivado) terlebih dahulu, dan menjalankan setidaknya tes primitif di atasnya. Bahkan bukan LED yang berkedip, tetapi umumnya satu gerbang XOR. Jika semua orang melakukan ini terlebih dahulu, maka di seminar kita akan membahas bukan masalah sepele seperti “Saya tidak punya driver untuk USB Blaster”, tetapi sesuatu yang lebih menarik, misalnya apa yang ditanyakan untuk wawancara posisi RTL Logic Designer di NVidia, AMD, Apple dan perusahaan lain.

Jadi, pertama-tama, seminar ini memiliki organisasi di github . Anda dapat mengkloning repositori ce2020labs dari sini dan menggunakan file di direktori before untuk menguji papan Anda, menginstal Quartus atau Vivado, driver, dan memecahkan masalah dengan pemrogram. Direktori berisi file untuk tujuh papan: lima papan dengan Intel FPGA (dua varian OMDAZZ / rzrd, dua varian ZEOWAA dan Terasic DE10-Lite), dan dua papan dengan Xilinx (Basys3 dan Nexys4).

Jika Anda tidak ingin menggunakan GitHub, Anda cukup mengunduh zip dari sini . Semua file ini akan bekerja dengan Quartus dan Vivado versi Windows dan Linux.

Untuk menginstal Quartus, Anda dapat menonton video terperinci dari Sergei Ivants, Dekan Fakultas Elektronik dan Teknologi Informasi Universitas Teknologi Nasional Chernihiv:

Video:

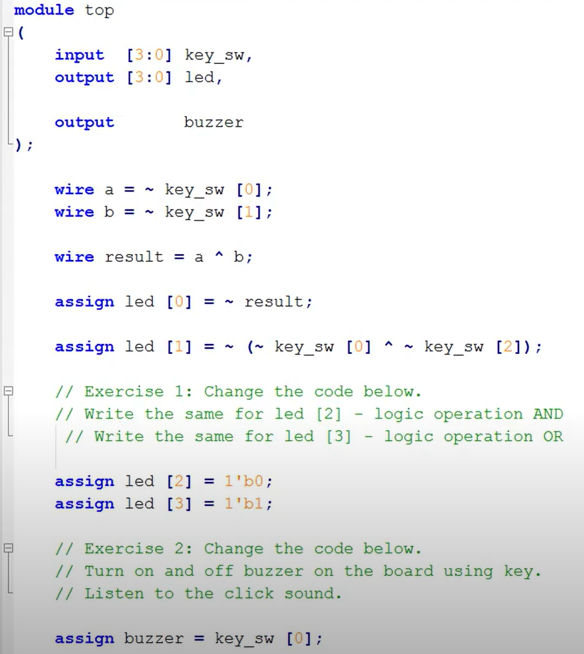

Dan video tentang sintesis contoh paling sederhana dari deskripsi dalam bahasa Verilog:

Dengan penjelasan rinci tentang apa:

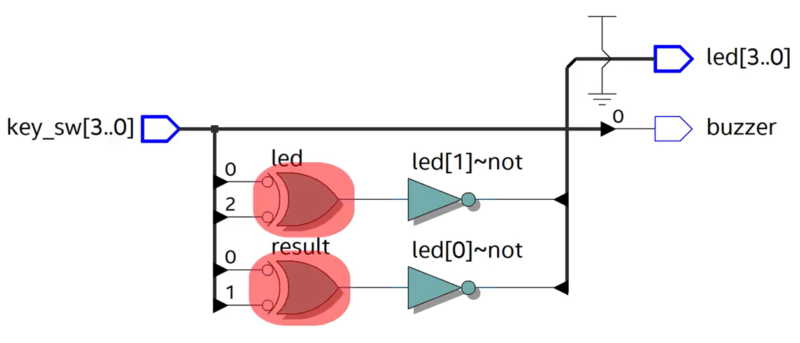

Satu-satunya masalah adalah bahwa video ini tidak mencakup penggunaan programmer dengan baik (dan masalah dengan drivernya). Oleh karena itu, Anda mungkin merasa berguna untuk menonton video lain, juga dari Sergey, di mana dia menjelaskan penggunaan USB Blaster setelah editor skematik. Di sini harus dikatakan bahwa entri skematik tidak lagi digunakan oleh perancang mikroelektronika digital pada awal 1990-an (semua orang beralih ke desain menggunakan bahasa deskripsi perangkat keras Verilog dan VHDL), tetapi Sergei tetap memutuskan untuk menunjukkan ini murni sehingga siswa yang mulai terlibat dalam desain digital akan segera secara intuitif Saya menyadari bahwa kami sedang mendesain sirkuit, dan tidak menulis program, meskipun kode di verlog mirip dengan kode dalam bahasa pemrograman.

Berikut adalah video dari entri skematik, yang di bagian akhir penggunaan programmer dijelaskan:

Sebelum, selama, dan setelah seminar di ChipEXPO di Skolkovo, kami akan terus memposting berbagai materi, tetapi untuk menonton semuanya (termasuk, misalnya, kuliah mini tentang bagaimana tim pengembang chip di Silicon Valley diatur), lebih baik mendaftar.