Baru-baru ini, saya menemukan salah satu opsi untuk papan debug dengan SoC Zynq XC7Z020. Setelah mencari di Internet untuk materi, a la how-to, dan mencoba memasukkan proyek minimal saya, saya menemukan bahwa ada sejumlah jebakan. Inilah yang ingin saya bicarakan di artikel ini. Siapa peduli - selamat datang di kucing.

Penting! Sebelum memulai cerita, saya ingin membuat reservasi terlebih dahulu bahwa tujuan utama yang saya kejar saat menulis artikel ini adalah untuk menunjukkan kepada para amatir di mana harus memulai ketika mempelajari papan debug berbasis Zynq. Saya bukan pengembang profesional untuk FPGA dan SoC Zynq dan saya dapat membuat kesalahan dalam penggunaan terminologi, tidak menggunakan cara yang paling optimal untuk memecahkan masalah, dll. Tetapi kritik konstruktif dan beralasan apa pun hanya diterima. Baiklah, ayo pergi ...

Jenis debugging apakah ini? Tunjukkan-beri tahu ...

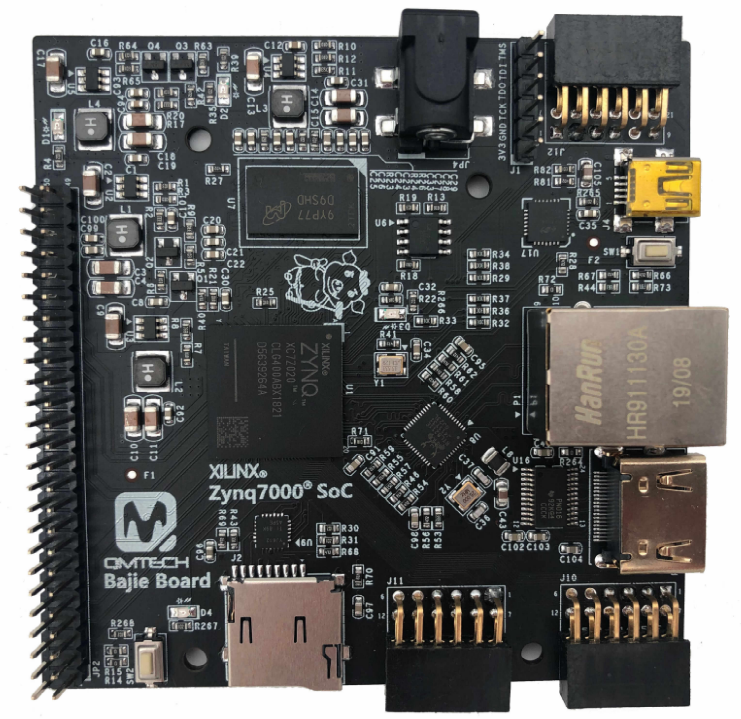

Untuk waktu yang sangat lama saya ingin bermain dengan SoC Zynq, tetapi tangan saya tidak bisa meraih. Tapi sekali lagi googling - saya melihat bahwa debugging dengan Zynq on board, dari QMTech, dijual dengan harga yang benar-benar waras, itu disebut Bajie Board. Debug tersedia dalam beberapa rasa dengan rasa Zynq SoC yang berbeda. Saya memilih versi XC7Z020 untuk diri saya sendiri dan langsung memesannya, setelah beberapa minggu saya sudah memilikinya.

, . , 5/2, mini-USB microSD Flash- SanDisk 16 Linux. , , USB-, Putty mini- Embedded Linux. Linux Zynq, , , ...

, -:

SoC: XC7Z020-1CLG400C

(datasheet:https://www.xilinx.com/support/documentation/data_sheets/ds190-Zynq-7000-Overview.pdf);

33,333 ;

DDR3 512 Micron, MT41K256M16TW-107:P;

micro SD;

FPGA TPS563201 ( 4.5V 17V, 3A);

50- Digilent PMOD , , 2,54 . ( , );

(PS);

RGMII Ethernet- Realtek RTL8211E-VL, PS;

, (PL) (PS);

HDMI- TI TPD12S016;

JTAG-;

.

, , - JTAG-. .

, Xilinx Vivado Xilinx SDK. , , Vivado . Xilinx SDK ( Vitis) .

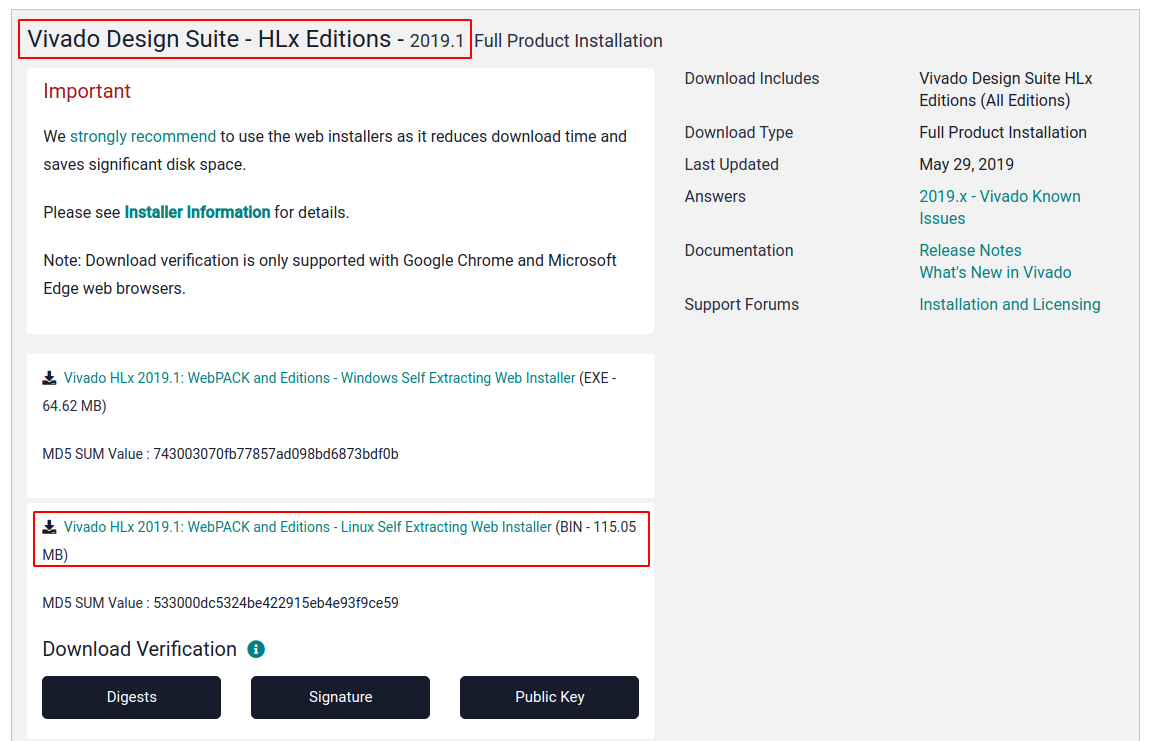

YouTube Vivado 2019.1 ( - , Xilinx SDK) - , 2020.2.

Xilinx Zynq - Xilinx, . , , Vivado - 2020.2, 2020.3 .. Versal SoC, Zynq.

, .. Linux - Vivado Archive - 2019.1 Vivado HLx 2019.1: WebPACK and Editions - Linux Self Extracting Web Installer Vivado Design Suite - HLx Editions - 2019.1. Windows - Windows Self Extracting Web Installer.

, :

chmod +x ~/Downloads/Xilinx_Vivado_SDK_Web_2019.1_0524_1430_Lin64.bin ~/Downloads/Xilinx_Vivado_SDK_Web_2019.1_0524_1430_Lin64.bin

.

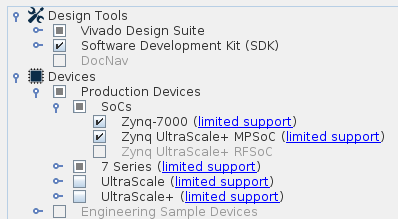

, ;

;

Vivado HL WebPACK;

, SoC Zynq .

16 -, .

Vivado JTAG-. Linux :

cd Xilinx2019.1/Vivado/2019.1/data/xicom/cable_drivers/lin64/install_script/install_drivers/

sudo ./install_drivers

6 JTAG- . :

cd ~/Xilinx2019.1/Vivado/2019.1/bin

./xsdb

xsdb% connect -host localhost

xsdb% jtag targets

1 Platform Cable USB 13724327082b01

2 arm_dap (idcode 4ba00477 irlen 4)

3 xc7z020 (idcode 23727093 irlen 6 fpga)

.

Hello, world “ ”

LED- .

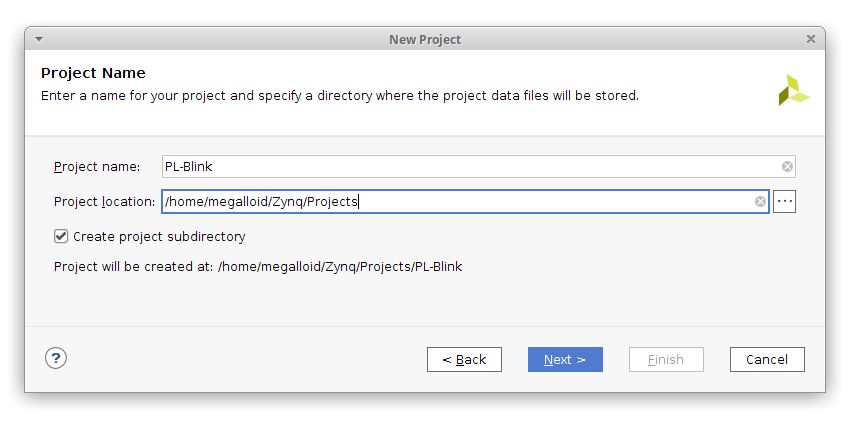

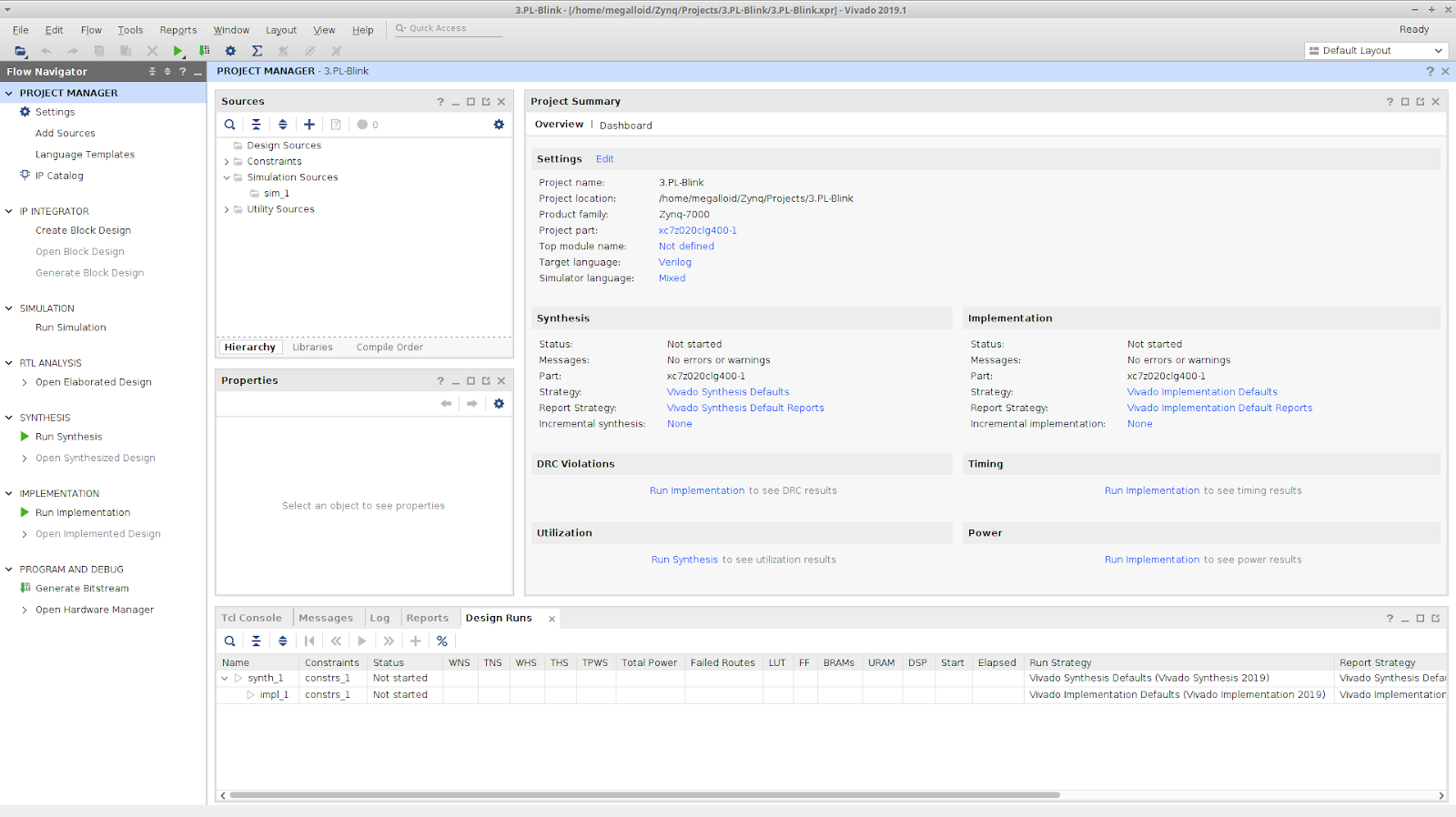

Vivado . File - Project - New…

, Next > PL-Blink.

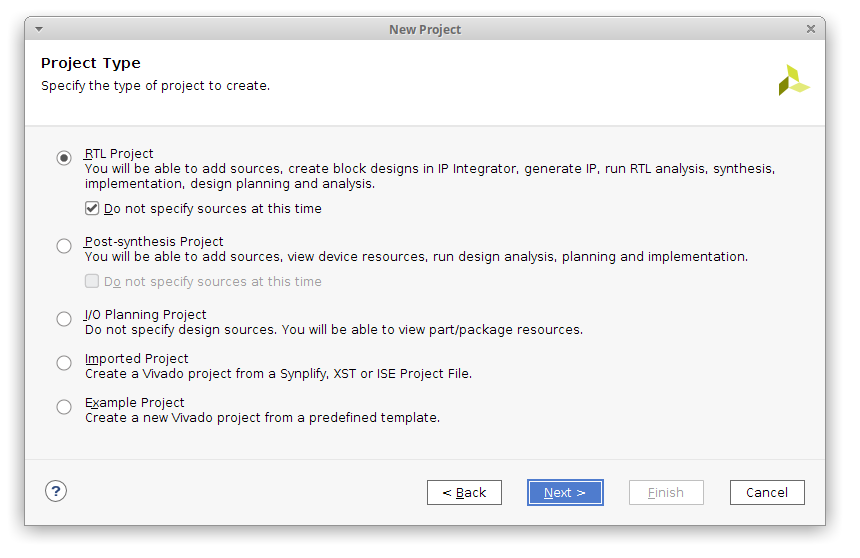

RTL Project Do not specify sources at this time.

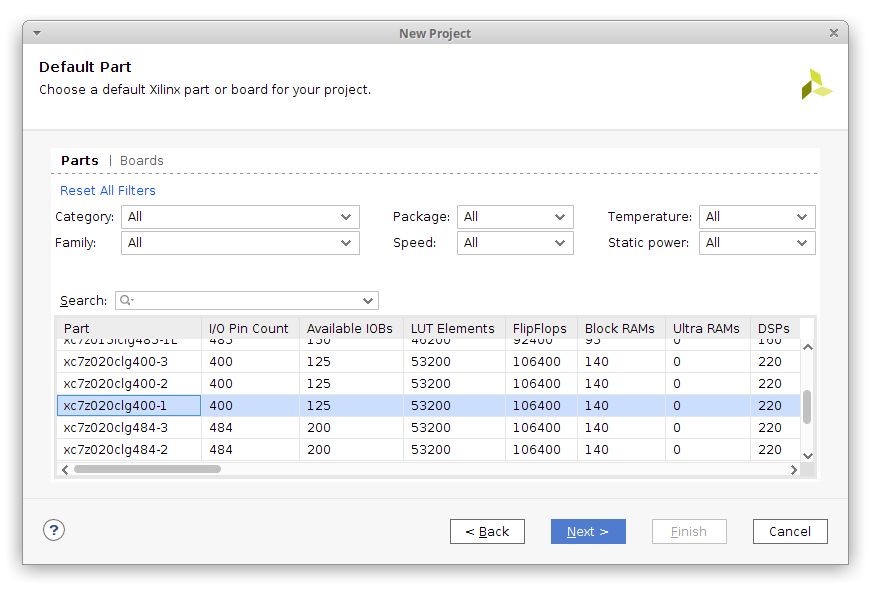

xc7z020clg400-1.

Finish.

Vivado !

, , , =)

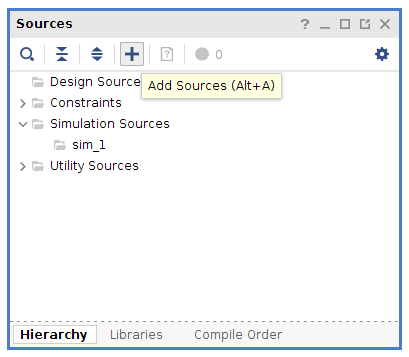

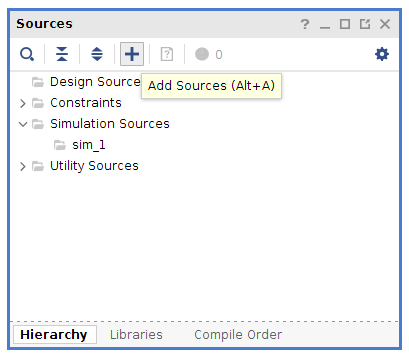

Sources Add Sources.

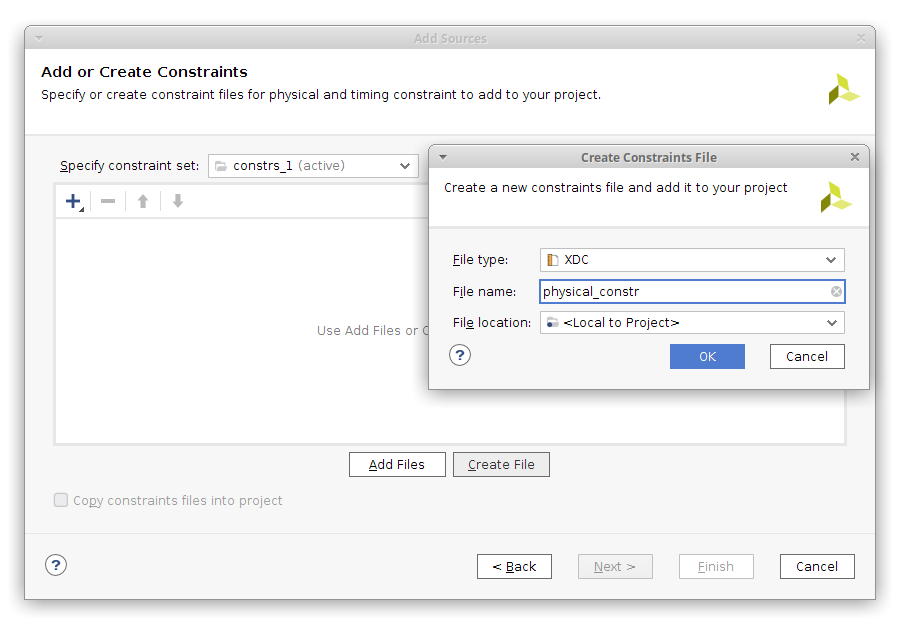

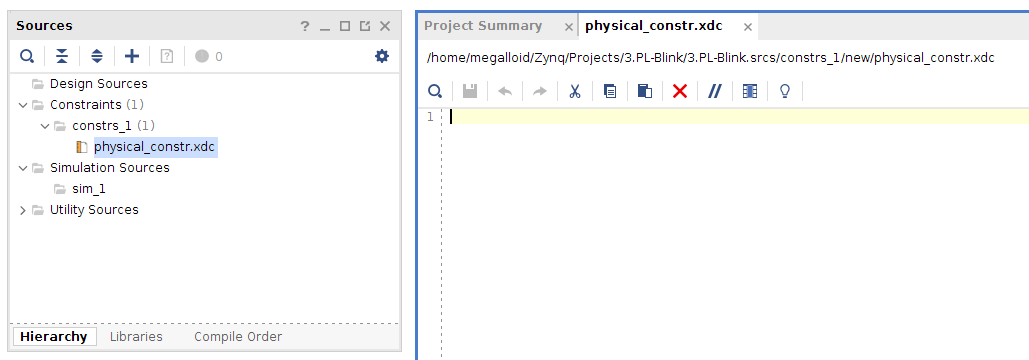

Add or create constraints.

Create file physical_constr. .

Finish Soures :

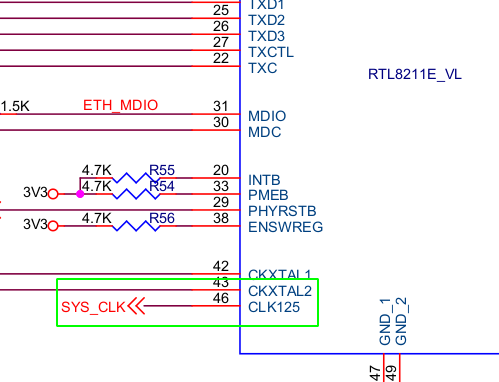

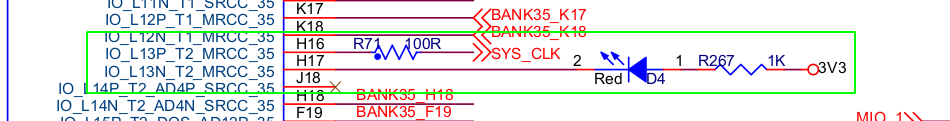

, , . , , Ethernet- RTL8211E-VL PLL, 125 H16 (IO_L13P_T2_MRCC_35). ? =)

, .

, , H17 (IO_L13N_T2_MRCC_35) , .

. constraints- :

# User LED and Clock

set_property IOSTANDARD LVCMOS33 [get_ports led_h17_d4]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN H17 [get_ports led_h17_d4]

set_property PACKAGE_PIN H16 [get_ports sys_clk]

, , , , .

, get_ports ( ). , Verilog-.

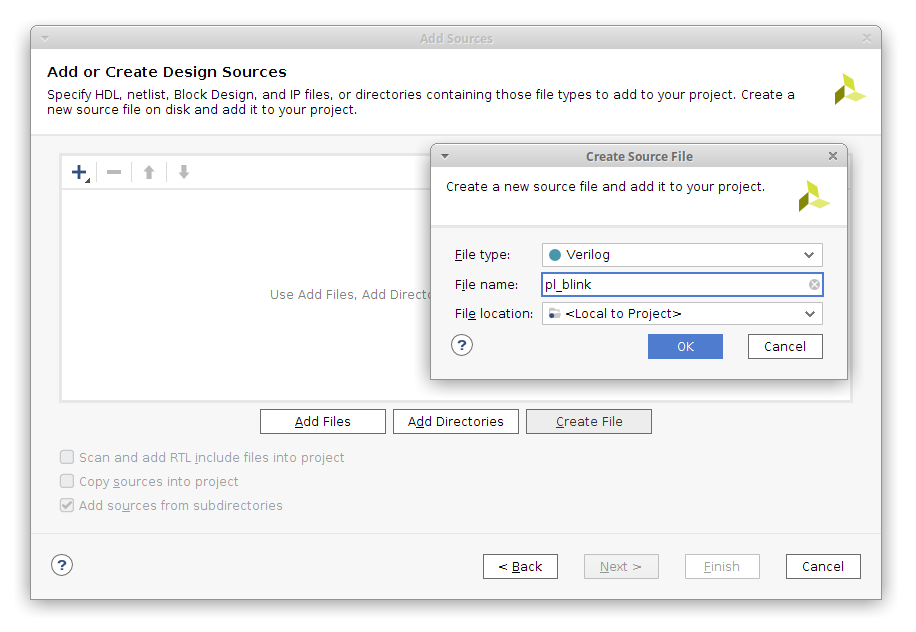

Design Source. Sources Add Sources.

Add or create design sources. Create File, , Verilog. Finish.

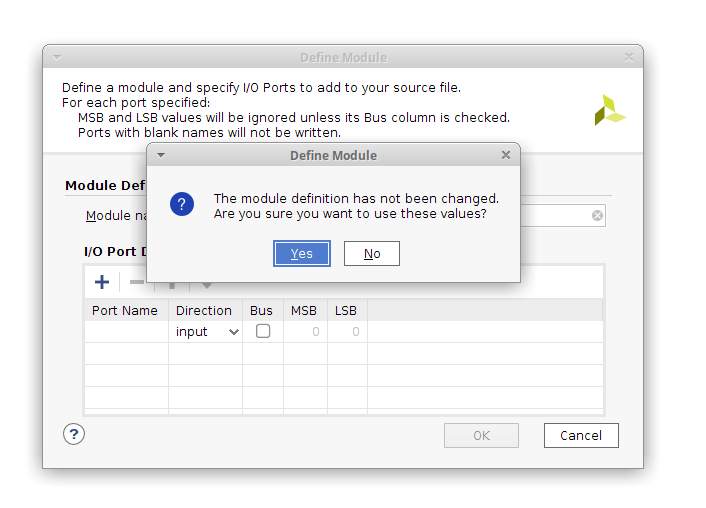

Yes.

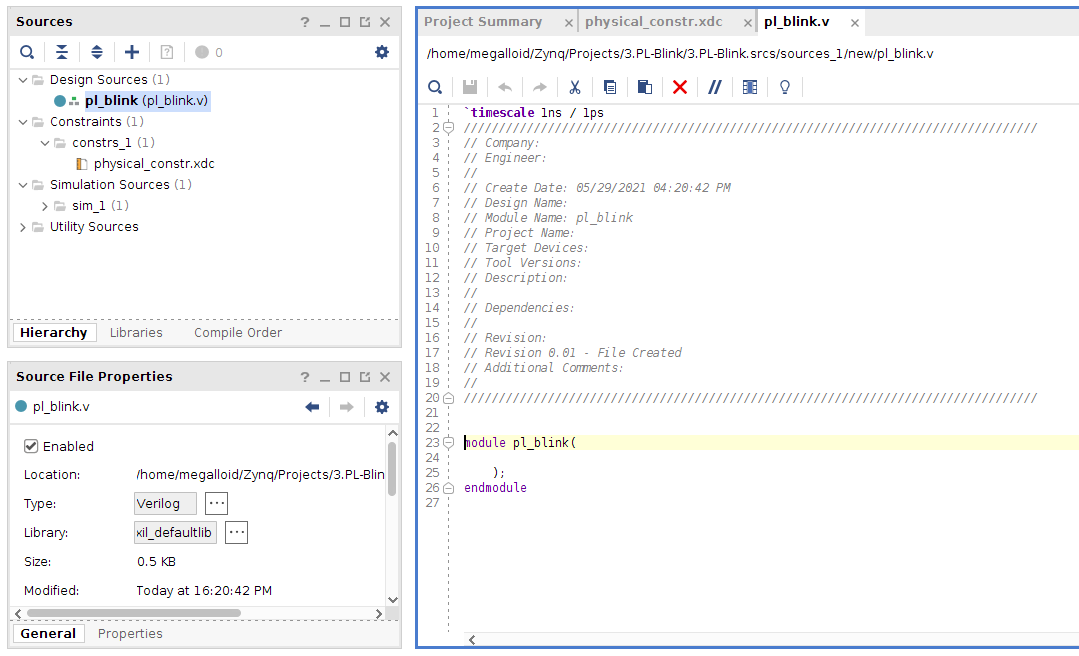

:

Verilog- :

// , Verilog.

// , .

`timescale 1ns / 1ps

// - ( ++)

module pl_blink(input sys_clk, output led_h17_d4);

//

reg r_led;

// ,

reg [31:0] counter;

//

initial begin

counter <= 32'b0; //

r_led <= 1'b0; //

end

// ,

always@(posedge sys_clk)

begin

counter <= counter + 1'b1; //

if(counter > 12000000) //

begin

r_led <= !r_led; //

counter <= 32'b0; //

end

end

assign led_h17_d4 = r_led; // ()

endmodule

Ctrl + S . , . - , Zynq .

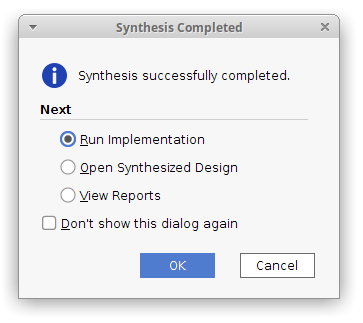

Run Synthesis . , :

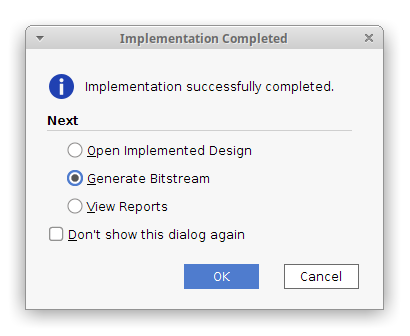

Run implementation . Generate Bitstream :

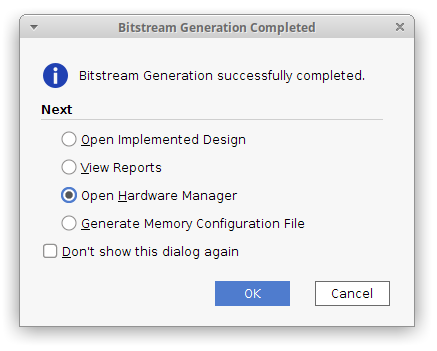

, , Open Hardware Manager :

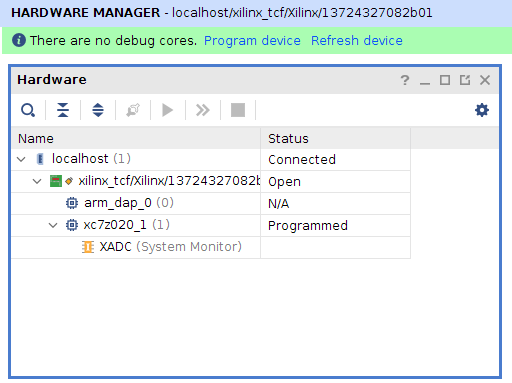

Hardware Manager Auto connect, :

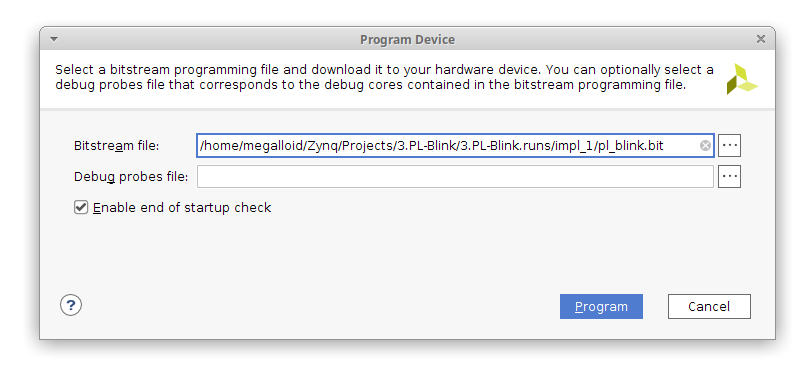

Di menu sebelah kiri atau dengan mengklik kanan xc7z020_1 di menu Hardware , klik item Program Device .

Di jendela berikutnya, pastikan bahwa jalur ke file bitstream ditentukan dengan benar dan klik tombol Program.

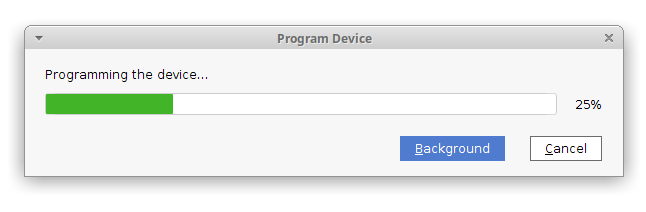

Program ini diunggah ke papan kami ...

Dan setelah beberapa saat, LED D2 di papan menyala, yang memberi tahu kami bahwa "FPGA SELESAI" dan di ujung lain papan kami melihat LED berkedip riang. =)

Secara umum, tugas tersebut dapat dianggap selesai. Saya rasa saat saya menguasai bahasa Verilog dan menyelesaikan masalah baru menggunakan papan ini, saya akan dapat menyenangkan Anda lagi.