Pentingnya masalah termal dapat dilihat dalam aturan praktis yang disederhanakan yang mengatakan bahwa setiap kenaikan suhu 10 pada C mempersingkat waktu kegagalan sebesar 2 kali lipat. Artinya, jika pada 55 pada sebuah chip akan bertahan 10 tahun, pada 65 sekitar Dengan hanya 5 argumen yang cukup untuk meningkatkan pembuangan panas dari chip, jika tidak bermain dalam keusangan yang direncanakan. Aturan ini jauh dari kebenaran tertinggi, tetapi secara kualitatif benar (Anda dapat membaca lebih lanjut, misalnya, di sini ).

Pengorganisasian heat sink hampir selalu merupakan proses overhead yang mempersulit perutean, sehingga harus direncanakan terlebih dahulu. Untuk melakukan ini, Anda perlu memahami apakah papan sirkuit tercetak itu sendiri dapat menangani unit pendingin. Produsen chip menunjukkan resistansi termal medium-kristal R θJA dalam dokumentasi . Tampaknya:

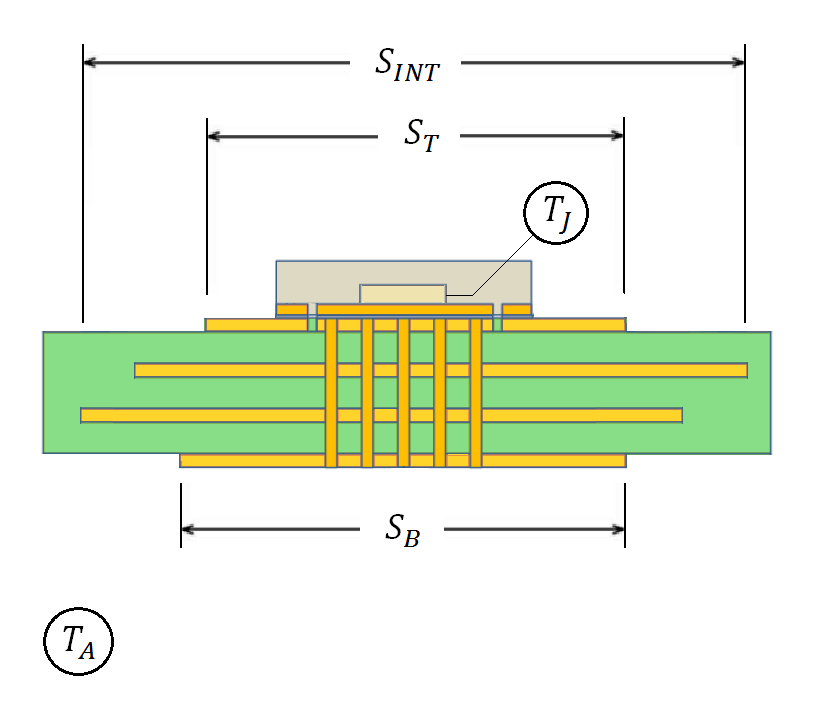

dan perkiraannya sudah siap. Tapi ini tidak sopan, sangat kasar. Resistansi termal sangat tergantung pada PCB. Dan apa yang ditunjukkan diperoleh dalam percobaan pada papan sirkuit tercetak standar (misalnya, seperti pada Gambar 1), yang, kemungkinan besar, akan sangat berbeda dari apa yang Anda dapatkan. Anggap saja Anda bisa mendapatkan heat sink yang jauh lebih baik dengan footprint yang lebih kecil.

Yang perlu diperhatikan adalah resistansi termal die-to-board R θJB atau R θJC (bawah) . Ini adalah sesuatu yang tidak bergantung pada pengembang dan ditentukan oleh tubuh dan desain internalnya. Tapi di sini, paling sering, pilihan kasing ditentukan oleh daya kehilangan panas, dan penurunan suhu utama akan ada di papan. Jadi, kami tulis ulang rumus di atas untuk kasus pembuangan panas melalui papan sebagai berikut:

di mana R θBA adalah resistansi termal papan sirkuit tercetak dengan parameter yang diberikan. Anda dapat menghitung resistansi ini berdasarkan model yang indah,

Segala sesuatu dengan persamaan ini baik-baik saja (kecuali untuk fungsi Bessel yang dimodifikasi), dan dapat diselesaikan untuk satu permukaan dengan konveksi (menghilangkan "2" di akar), tetapi hanya papan yang paling sering tanpa simetri radial dan tidak homogen, tetapi juga panas disuplai secara tidak merata di sepanjang internal radius. Jadi, Anda perlu beradaptasi. Dua pertanyaan pertama diselesaikan dengan membaginya menjadi zona annular dengan sifat homogen dengan luas yang sama. Untuk mengatasi yang terakhir, Anda perlu membuat model perkiraan rangkaian resistansi termal. Gambar 3 menunjukkan apa yang disarankan dalam artikel asli. Diusulkan untuk memecah papan menjadi tiga zona: zona di bawah sirkuit mikro, zona dengan poligon di lapisan luar, dan zona dengan hanya poligon di lapisan dalam. Hanya konduktor yang terhubung langsung ke sirkuit mikro yang diperhitungkan (secara kondisional, "dering").

Diusulkan untuk rata-rata poligon atas dan bawah dan mengambil rata-rata luas metalisasi. Saya tidak begitu setuju dengan ini, karena efek pada pembuangan panas dari lapisan-lapisan ini jelas berbeda, ditambah lagi mereka dapat sangat berbeda dalam area (yang lebih rendah seringkali akan lebih besar di area). Oleh karena itu, saya membagi papan menjadi dua bagian atas dan bawah dan melakukan perhitungan untuk setiap bagian secara terpisah.

Artikel ini berisi banyak grafik dengan pengaruh berbagai parameter, ada baiknya untuk melihatnya. Saya mengkalibrasi pendekatan saya untuk memisahkan papan pada grafik ini (Gambar 4) - mereka masing-masing untuk paket QFN5X5, QFN6X6 dan QFN3X3. Ketika papan sangat besar, grafik "jatuh" pada batas yang terkait dengan ketahanan termal vias, tetapi parameternya tidak ditentukan. Saya mengambil diameter 450 mikron, ketebalan dinding 20 mikron, tanpa mengisi.

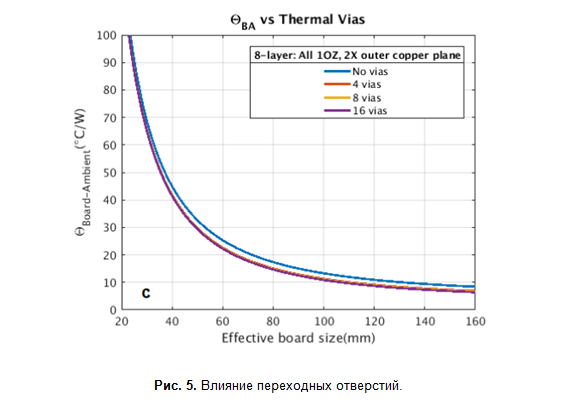

Dapat dilihat bahwa modelnya berkorelasi, tetapi saya tidak mencoba mencapai 100% kebetulan, karena semua data input masih hilang. Selain itu, ada momen aneh dengan vias (Gambar 5), ketidakhadiran mereka secara praktis tidak mempengaruhi ketahanan termal, yang tidak terlalu intuitif.

Bahkan pada grafik yang lebih rendah pada Gambar 4, Anda dapat melihat dua baris data, di mana saya menghitung model dua zona dengan dua metode: menggunakan perkalian matriks, seperti yang dijelaskan dalam artikel AND8222 / D, dan menggunakan model, seperti pada Gambar 3, hanya zona di bawah sirkuit mikro yang dibuang (itu tidak berkontribusi pada perlawanan). Dapat dilihat bahwa grafik dari artikel menuju ke asimtot yang kurang lebih sama, seolah-olah pengaruh vias tidak ada. Ini bagi saya menjadi faktor lain bahwa ada sesuatu yang salah dalam model mereka, dengan mempertimbangkan pengaruh vias (atau saya tidak mengerti sesuatu).

Kalkulator ternyata berguna setidaknya dalam arti memungkinkan untuk berpindah dari gagasan kualitatif tentang pengaruh berbagai parameter ke perkiraan kuantitatif. Dapat disimpulkan bahwa ketahanan termal papan dapat didorong ke wilayah 10 oC / W bahkan dengan konveksi alami. Untuk pembuangan, 2-3 W sudah cukup. Catatan berguna lainnya adalah bahwa hanya logam yang terhubung langsung ke sirkuit mikro yang memainkan peran penting dalam unit pendingin. Meskipun, tentu saja, semakin besar fraksi volume tembaga di papan, semakin tinggi konduktivitas termal efektifnya. Atas dasar kalkulator ini, Anda dapat meningkatkan keberadaan heatsink pada sirkuit mikro dan heat sink ke kasing, saya juga akan melakukan ini. Jika ada yang menarik, akan saya bagikan di publikasi berikutnya.