Artikel sebelumnya dalam seri ini

Sebenarnya, artikel ini muncul sebagai file DOC pada bulan Juni. Kemudian satu blok lima artikel ditulis secara bersamaan. Tetapi mengunggah file DOC ke Habr adalah tugas lain. Oleh karena itu, kebetulan waktu untuk itu muncul hanya sekarang (dan dua lagi mendekam dalam antisipasi). Saat mengunggah, saya perhatikan bahwa jika Anda tidak menyukai artikel sebelumnya, yang ini terlihat agak membosankan. Oleh karena itu, jika ada keinginan seperti itu, segarkan setidaknya artikel terakhir dalam memori Anda, atau lebih baik keduanya ( "Membuat kepala penganalisis bus USB ..." dan "Mensimulasikan perilaku proyek Quartus ..." ).

pengantar

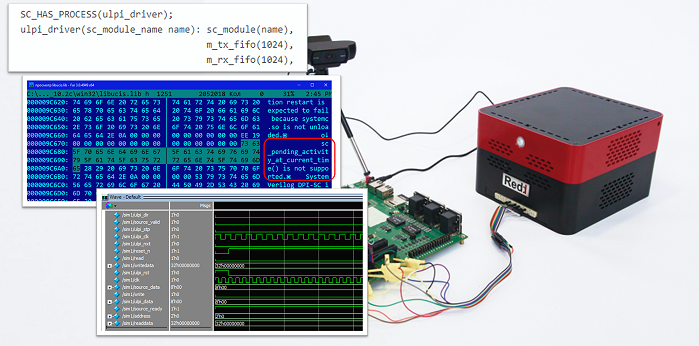

Jadi, model yang sudah jadi, di mana saya bisa mendapatkannya? Ada sebuah proyek yang memecahkan masalah yang persis sama dengan penganalisis yang kami kembangkan, tetapi memiliki beberapa fitur. Fitur pertama adalah untuk FPGA Xilinx. Kedua, itu sama sekali tidak berdokumen. Ini bekerja entah bagaimana. Anda bahkan dapat membeli papan tempat memotong roti yang sudah jadi, mengisinya dengan kode biner yang sudah jadi ... dan mendapatkan beberapa fungsionalitas. Siapa pun yang membutuhkan perangkat dengan biaya berapa pun dapat mengikuti jalur ini. Tapi tidak ada yang tahu bagaimana mengembangkannya. Proyek itu ada di sini . Di direktori \ ulpi_wrapper \ testbenchada sekumpulan file untuk menguji subsistem pembungkus di sekitar ULPI. Mereka merekomendasikan pemodelan di lingkungan Icarus Verilog, tetapi saya mencari-cari dan tidak menemukan deskripsi yang masuk akal di permukaan tentang cara melakukan ini dalam bahasa SystemC. Oleh karena itu, saya memutuskan untuk terus bekerja di lingkungan ModelSim. Jika saya tahu bagaimana ini akan berakhir ... Tapi saya tidak tahu. Oleh karena itu, saya memulai penelitian. Selama presentasi, keberhasilan dan kegagalan akan ditampilkan. Mari kita mulai dengan kegagalan, sehingga setiap orang dapat melihat bagaimana cara untuk tidak melakukannya.

Upaya gagal untuk melakukan segala sesuatu "langsung"

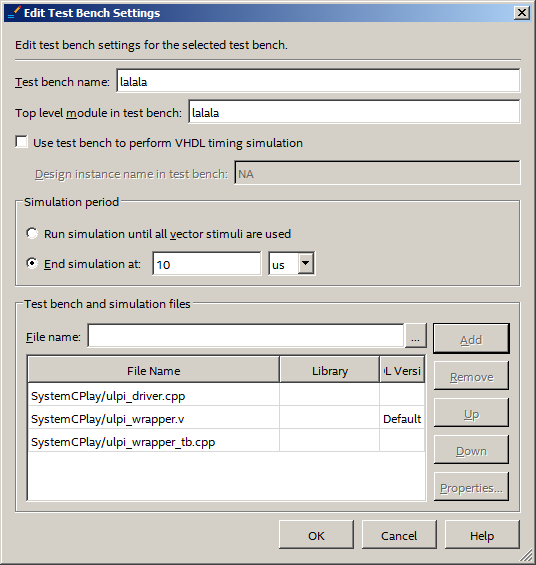

Awalnya saya memutuskan untuk mengambil contoh yang sudah jadi dan menjalankannya melalui pemodelan. Dengan gerakan tangan saya yang biasa (dan kami memasukkan tangan kami di artikel terakhir ), saya membuat rangkaian pengujian yang berisi file di Verilog dan SystemC. Ternyata sesuatu seperti ini: Saya

meluncurkan ModelSim dan saya tidak melihat apa pun dalam kelompok kerja yang akan terkait dengan SystemC. Saya melihat kode Verilogo, tetapi kode Sishny tidak.

Jika Anda melihat log, Anda dapat melihat bahwa mereka tidak mencoba mengumpulkannya. Apa masalahnya?

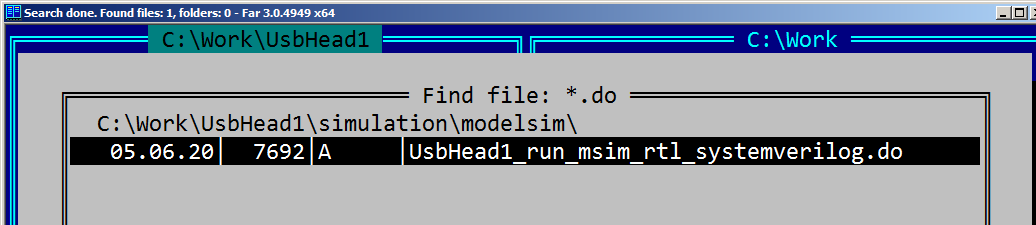

Informasi berguna tentang cara mengonfigurasi file * .do

File * .do dikenal untuk menjalankan ModelSim. Tapi sebagai pecinta melakukan segalanya dengan "tikus", saya tidak pernah melihat ke dalam dirinya. Mari kita cari dan buka! Hanya ada satu file seperti itu di direktori proyek. Ini mungkin yang kita butuhkan.

Kami membukanya. Pada awalnya - perakitan semua jenis item layanan dan file yang disertakan dalam proyek.

Perhatikan teksnya

transcript on

if ![file isdirectory verilog_libs] {

file mkdir verilog_libs

}

if ![file isdirectory vhdl_libs] {

file mkdir vhdl_libs

}

vlib verilog_libs/altera_ver

vmap altera_ver ./verilog_libs/altera_ver

vlog -vlog01compat -work altera_ver {c:/intelfpga_lite/17.1/quartus/eda/sim_lib/altera_primitives.v}

vlib verilog_libs/lpm_ver

vmap lpm_ver ./verilog_libs/lpm_ver

vlog -vlog01compat -work lpm_ver {c:/intelfpga_lite/17.1/quartus/eda/sim_lib/220model.v}

vlib verilog_libs/sgate_ver

vmap sgate_ver ./verilog_libs/sgate_ver

vlog -vlog01compat -work sgate_ver {c:/intelfpga_lite/17.1/quartus/eda/sim_lib/sgate.v}

Tetapi pada akhirnya - jelas perakitan hal-hal yang kita butuhkan, saya menilai ini dengan nama file ulpi_wrapper.v :

vlog -vlog01compat -work work +incdir+C:/Work/UsbHead1/SystemCPlay {C:/Work/UsbHead1/SystemCPlay/ulpi_wrapper.v}

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cycloneive_ver -L rtl_work -L work -L UsbHead1 -voptargs="+acc" lalala

add wave *

view structure

view signals

run 10 us

Betulkah. Ada perakitan modul Verilog, dan tidak ada petunjuk perakitan modul di SystemC. Satu-satunya hal yang disayangkan adalah file DO ini secara otomatis dibuat setiap kali Anda memulai simulasi, jadi Anda tidak bisa hanya mengambil dan mengeditnya. Itu dibuat oleh skrip TCL yang sangat kompleks. Tidak ada keinginan untuk mengaturnya. Tetapi setelah artikel tentang kuartal yang ceria , mungkin jelas bahwa hal sepele seperti itu bukanlah alasan untuk menyerah. Tentunya semuanya sudah ada. Satu-satunya hal yang disayangkan adalah dokumentasi mengatakan bahwa "Anda dapat membuat skrip dengan cara ini, atau Anda dapat melakukan ini", dan tidak ada petunjuk tentang contoh. Baiklah, mari kita simpulkan semuanya secara eksperimental. Buat file C: \ Work \ UsbHead1 \ SystemCPlay \ myrun.do dan coba transfer kontrol ke file tersebut. Pertama, kami mencoba melakukannya seperti ini:

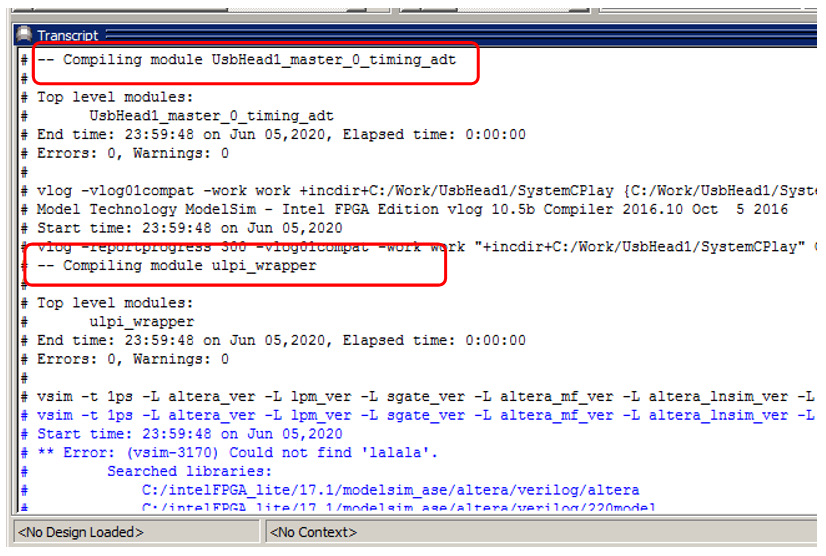

File DO utama masih terus dibuat, tetapi akhirnya menjadi seperti ini:

vlog -sv -work UsbHead1 +incdir+C:/Work/UsbHead1/UsbHead1/synthesis/submodules {C:/Work/UsbHead1/UsbHead1/synthesis/submodules/UsbHead1_master_0_b2p_adapter.sv}

vlog -sv -work UsbHead1 +incdir+C:/Work/UsbHead1/UsbHead1/synthesis/submodules {C:/Work/UsbHead1/UsbHead1/synthesis/submodules/UsbHead1_master_0_timing_adt.sv}

vlog -vlog01compat -work work +incdir+C:/Work/UsbHead1/SystemCPlay {C:/Work/UsbHead1/SystemCPlay/ulpi_wrapper.v}

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cycloneive_ver -L rtl_work -L work -L UsbHead1 -voptargs="+acc" lalala

do C:/Work/UsbHead1/SystemCPlay/myrun.do

Kami melihat bahwa file Verilog masih dikompilasi, kemudian proses pemodelan masih dimulai (meskipun saya melihat ini selama pengujian berjalan, tetapi sekarang saya dapat mengatakan dengan pasti bahwa perintah vsim memulai proses ini), setelah itu kontrol ditransfer ke kami naskah. Skrip ini harus mengontrol proses tampilan. Tapi kami masih tidak bisa mengatur majelis. Jika file yang dikumpulkan tidak cukup, sistem akan jatuh karena kesalahan sebelum kita diizinkan untuk melakukan apapun. Baiklah, bagus, mari kita coba pengaturan terakhir.

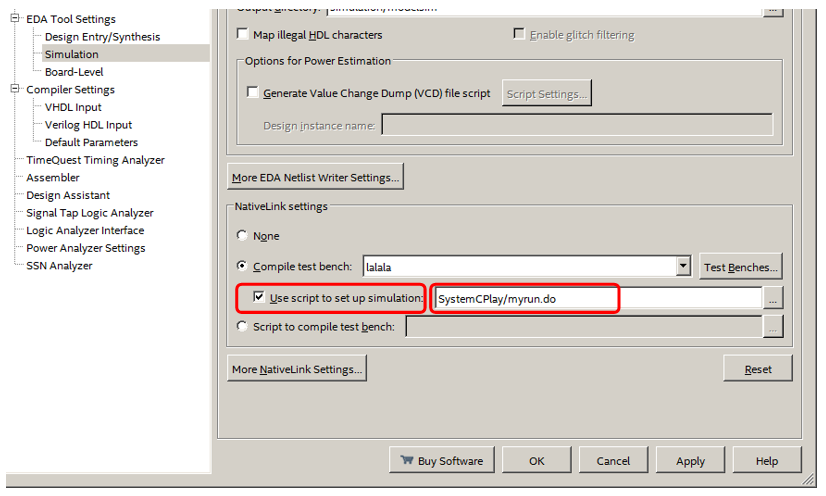

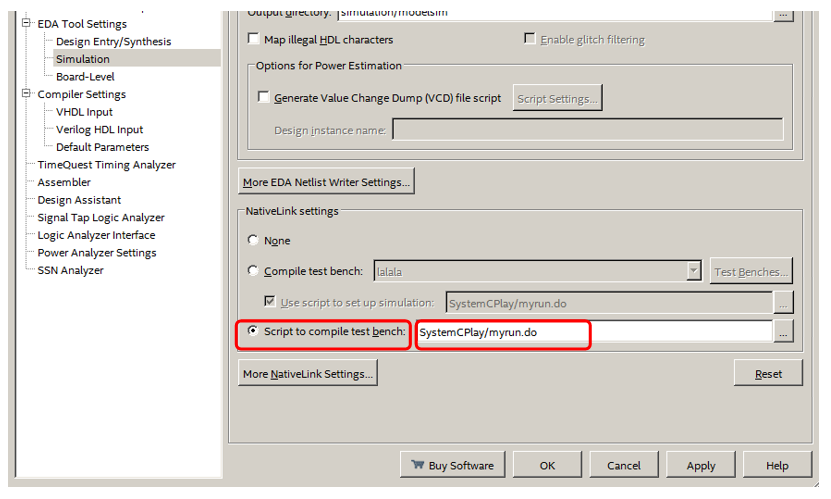

Dan di sinilah kesenangan dimulai. Sangat penting bahwa saya akan membingkainya.

Saya memilih skrip, tetapi tidak dipilih. Saya masuk ke pengaturan (saya memiliki opsi yang dipilih sebelumnya). Saya memilih, bukan dipilih. Dan - bahkan sampai membiru di wajah. Sampai saya menyadarinya, sampai saya menemukan cara menang - saya membunuh malam itu! Ternyata jika Anda baru memilih file, tombol Terapkan akan tetap berwarna abu-abu. Dan perubahan itu tidak akan diingat. Sangat penting untuk membuat tombol Apply menjadi hitam dengan mengedit parameter dialog lainnya! Pada gambar di atas, benar-benar hitam. Jika tetap berwarna abu-abu, perubahan tidak akan disimpan, dan semuanya tidak akan dikonfigurasi ulang untuk menggunakan skrip.

Naskahnya masih dalam proses, tetapi akhirnya menjadi lebih nyaman bagi kami.

vlog -sv -work UsbHead1 +incdir+C:/Work/UsbHead1/UsbHead1/synthesis/submodules {C:/Work/UsbHead1/UsbHead1/synthesis/submodules/UsbHead1_master_0_timing_adt.sv}

do "C:/Work/UsbHead1/SystemCPlay/myrun.do"

Akhirnya, proses membangun kode sumber untuk proyek ini sepenuhnya bergantung pada belas kasihan kami! Hebat! Pada saat itu, saya hanya dapat menemukan Verifikasi SystemC dengan dokumen ModelSim yang ditulis untuk Xilinx. Tapi ModelSim ada di Afrika ModelSim. Menggunakan contoh dari dokumen ini dan contoh file DO yang dibuat pada percobaan sebelumnya, saya membuat teks skrip berikut (jangan khawatir dengan banyaknya kunci, di bawah ini kami akan membuang hampir semuanya, kami juga akan mengganti jalur absolut dengan yang relatif nanti, pada tahap ini saya baru saja menarik semuanya dari contoh dan sampel yang dibuat secara otomatis).

vlog -vlog01compat -work work +incdir+C:/Work/UsbHead1/SystemCPlay {C:/Work/UsbHead1/SystemCPlay/ulpi_wrapper.v}

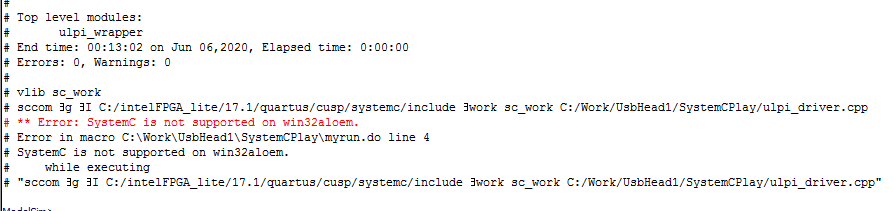

vlib sc_work

sccom –g –I C:/intelFPGA_lite/17.1/quartus/cusp/systemc/include –work sc_work C:/Work/UsbHead1/SystemCPlay/ulpi_driver.cpp

Drum roll ... Dan ModelSim menyatakan kepada kita:

Jika kita menghilangkan semua kata-kata cabul, maka saya tidak punya apa-apa untuk dikatakan ... Tapi jalan seperti itu telah dilewati! Dan di mana mendapatkan model ULPI lain? Tentu saja, saya membuat kesepakatan dengan teman-teman asing yang secara profesional terlibat dalam proyek serius untuk FPGA. Khusus untuk saya, mereka membuka akses jarak jauh ke mesin dengan ModelSim berlisensi untuk akhir pekan. Pancake kedua juga ternyata menggumpal: versi 64-bit, bahkan dalam bentuk berlisensi, tidak berfungsi dengan SystemC. Tetapi pada akhirnya, saya bisa bermain-main dengan versi 32-bit dari ModelSim berlisensi. Oleh karena itu, kami melanjutkan ceritanya ...

Beberapa kata tentang dokumentasi

Begitu. Sekarang setelah saya memiliki akses ke perangkat lunak berlisensi, saatnya berbicara tentang di mana mencari informasi dan di mana mendapatkan inspirasi. Di web, informasi tentang bahasa tersebut agak samar. Tetapi dalam pengiriman sistem, ada direktori berguna berikut:

C: \ modeltech_10.2c \ docs \ pdfdocs - dokumentasi, termasuk file dalam format PDF. Saya menyukai file modelsim_se_ref.pdf (Manual Referensi Perintah ModelSim SE), modelsim_se_user.pdf (Panduan Pengguna ModelSim SE), dan modelsim_se_tut.pdf (Tutorial ModelSim SE). Tidak banyak tentang bahasa itu sendiri, tetapi tentang bagaimana menghubungkan file dan bagaimana menyelesaikan masalah dialek - cukup.

Selanjutnya, direktori berguna C: \ modeltech_10.2c \ contoh... Ada contoh file * .do yang sudah jadi dan file cpp dan h yang sudah jadi. Contoh yang paling berguna bagi kami adalah C: \ modeltech_10.2c \ example \ systemc \ vlog_sc . Ini menunjukkan kepada Anda bagaimana mengakses kode SystemC dari kode Verilog. Kami, pada akhirnya, akan pergi persis seperti ini.

Direktori C: \ modeltech_10.2c \ include \ systemc berisi kode sumber untuk pustaka tipe bahasa. Bukan referensi yang buruk. Seperti yang mereka katakan, ada ikan untuk penyakit tanpa ikan dan kanker.

Semuanya dari katalog. Sekarang judul buku yang luar biasa, dari mana Anda dapat belajar banyak tentang bahasa dan tentang metode pemrograman di dalamnya. SystemC - From the Ground Up, Edisi Kedua. Oleh David C. Black, Jack Donovan, Bill Bunton, Anna Keist.

Dialek SystemC

Begitu. Setelah mendapatkan akses ke sistem kerja, saya dengan senang hati menyusun proyek, sesuai dengan skrip yang dibuat sebelumnya. Dia berkumpul tanpa kesalahan! Model pertama dari GitHub setuju untuk bekerja dengan kami! Ingin menjalankan benchmark, saya menambahkan file ulpi_wrapper_tb.cpp dari direktori yang sama ke proyek dan mendapat banyak kesalahan. Katakanlah ada kesalahan di baris:

m_vpi_handle = vpi_handle_by_name ((const char *) name, NULL);

sulit untuk diperbaiki, tetapi masih memungkinkan. Tapi garisnya

// Update systemC TB

if(sc_pending_activity())

sc_start((int)(time_value-m_last_time),SC_NS);

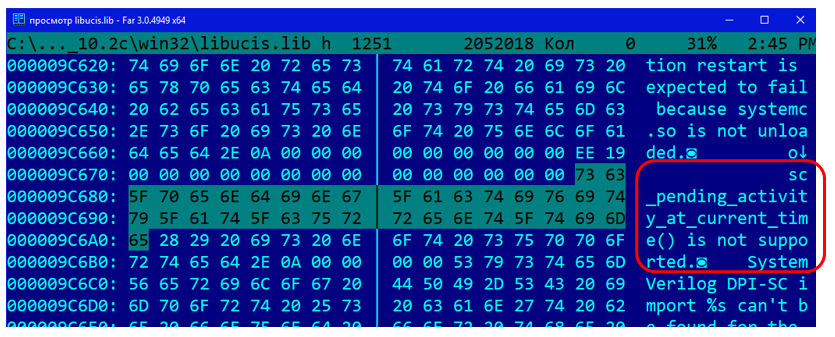

membayangkan pikiran buruk. Tidak ada fungsi sc_pending_activity () di perpustakaan. Ada fungsi sc_pending_activity_at_current_time () , tapi saya bahkan tidak repot - repot menghadapinya . Alih-alih seribu kata penjelasan, saya akan memberikan dump:

Dan ada 44 file dengan teks ini (* .exe, * .dll, dll.).

Anda dapat mencoba menulis ulang semuanya ... Tetapi apakah itu perlu? Izinkan saya mengingatkan Anda bahwa saya benar-benar memulai semua ini, karena saya ingin menggunakan semua yang sudah siap. Saya dapat mengembangkan semuanya dalam lingkungan gratis dengan SystemVerilog murni, jika saya benar-benar menghabiskan banyak waktu ... Saya datang ke sini agar tidak membuang waktu, tetapi untuk menghemat! Tapi sebenarnya ... Hal utama adalah jangan melupakan apa yang kita lakukan. Kami ingin menggunakan model bus ULPI. Dia menenangkan diri. Masalah muncul ketika mencoba membangun sistem pengujian lengkap dari contoh ... Mengapa ini? Nah, sistem lengkapnya tidak berfungsi, dan oke. Kami akan menguasai satu model, tanpa melihat pengoperasian sistem, dengan trial and error.

Menghilangkan kesalahpahaman berbasis dialek

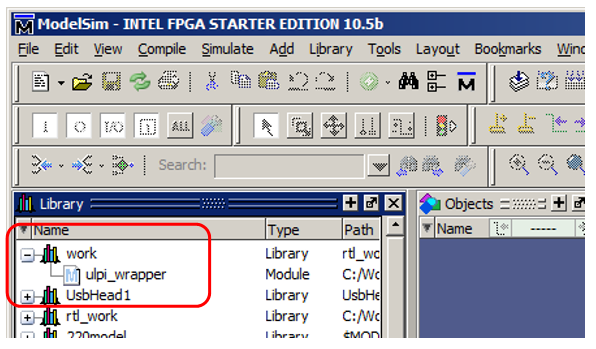

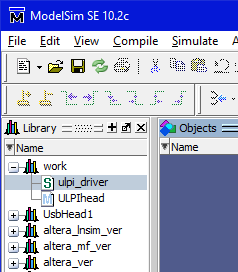

Begitu. Kami akan melakukan sistem campuran. Modul dengan model akan ditulis dalam bahasa SystemC, dan saya akan mengirimkan tindakan pengujian padanya dan modul yang sedang dikembangkan dalam bahasa Verilog. Artinya, Anda perlu membuat modul ulpi_driver muncul di grup kerja .

Memeriksa contoh file * .do dari pengiriman ModelSim, saya sangat menyederhanakan skripnya, dan pada akhirnya, saya membuat ini:

vlog +../../SystemCPlay {../../MyCores/ULPIhead.sv}

sccom -g ../../SystemCPlay/ulpi_driver.cpp

sccom -link

Tidak ada kesalahan, tetapi modul juga tidak muncul di grup. Memeriksa file contoh (ingat, contoh terbaik yang mengimplementasikan dengan tepat pencampuran bahasa ini ada di direktori C: \ modeltech_10.2c \ example \ systemc \ vlog_sc ), saya menyadari bahwa baris berikut harus ditambahkan ke akhir file ulpi_driver.cpp :

SC_MODULE_EXPORT(ulpi_driver);

Dokumentasi untuk ModelSim mengatakan bahwa ini adalah fitur dialek. Dan voila! Ini dia, modul kami:

Benar, menu Buat Gelombang (kami membahas menu ini di artikel terakhir ) tidak tersedia untuk itu. Dan dia tidak memiliki port. Secara historis, saya pertama kali berurusan dengan port, tetapi secara metodis - saya akan menunda cerita tentang mereka untuk nanti. Jika tidak, Anda harus mengedit kode dua kali. Untuk menghindari hal tersebut, mari kita lakukan sedikit persiapan terlebih dahulu.

Membuat generator jam

Ternyata modelnya memiliki beberapa perbedaan dari ULPI asli. Perbedaan pertama adalah bahwa clock 66 MHz harus dihasilkan oleh chip. Apa yang kita lihat di model?

sc_in<bool> clk_i;

Kekacauan! Ayo mulai pengerjaan ulang! Semua pekerjaan, kecuali dinyatakan lain, dilakukan di file ulpi_driver.h.

Ubah jenis port. Dulu:

sc_in<bool> clk_i;

menjadi (Saya juga mengubah nama port):

sc_inout<bool> clk;

Saya belajar dari buku bahwa generator nyata dimasukkan dengan menambahkan variabel:

sc_clock oscillator;

Kami mengatur parameter di konstruktor. Hasilnya, konstruktor berbentuk:

//-------------------------------------------------------------

// Constructor

//-------------------------------------------------------------

SC_HAS_PROCESS(ulpi_driver);

ulpi_driver(sc_module_name name): sc_module(name),

m_tx_fifo(1024),

m_rx_fifo(1024),

oscillator ("clk66",sc_time(15,SC_NS))

{

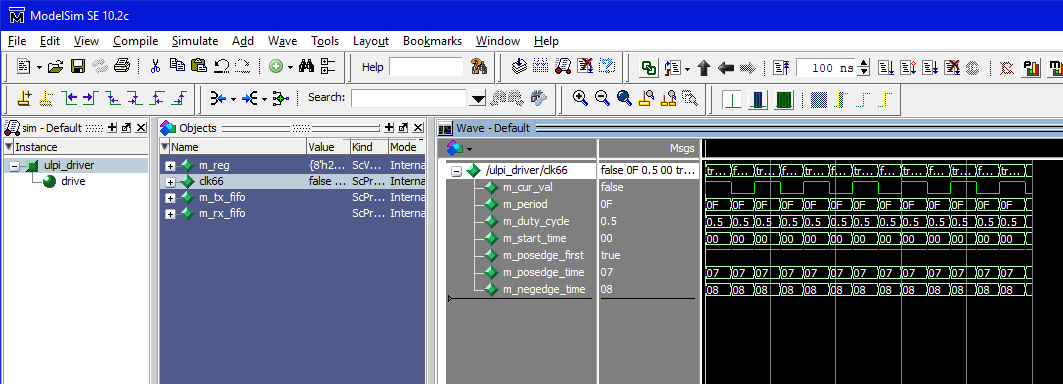

Baris terakhir hanya untuk ini. Jika mau, Anda bahkan dapat memulai simulasi, klik dua kali pada modul usb_driver , kemudian tarik clk66 ke gubuk sementara dan jalankan sedikit proses simulasi . Kita sudah melihat cara kerja generator:

Jangan lupa untuk mengubah nama sinyal clock di tempat thread utama dimulai. Dulu:

SC_CTHREAD(drive, clk_i.pos());

Menjadi:

SC_CTHREAD(drive, clk.pos());

Tautan internal telah diganti. Tapi betapa indahnya membawa sinyal ke luar, saya tidak menemukannya. Mungkin saya hanya kurang kualifikasi. Tetapi dengan satu atau lain cara, dan semua upaya untuk menarik pelabuhan keluar, belum dimahkotai dengan sukses. Selalu ada sesuatu di jalan. Saya bahkan menemukan sebuah diskusi di salah satu forum di mana penulis perlu melakukan hal yang sama. Tim memutuskan bahwa itu hanya dapat diteruskan ke port input. Tapi kita harus keluar! Oleh karena itu, kami melakukan ini.

Tambahkan fungsi aliran di bawah konstruktor:

void clkThread(void)

{

while (true)

{

wait(oscillator.posedge_event());

clk.write (true);

wait(oscillator.negedge_event());

clk.write (false);

}

}

Dan tambahkan tautan ke sana di konstruktor kelas:

SC_THREAD(clkThread);

Izinkan saya menunjukkan kepada Anda area konstruktor saat ini, jadi ada pandangan holistik dari hasil saat ini:

SC_HAS_PROCESS(ulpi_driver);

ulpi_driver(sc_module_name name): sc_module(name),

m_tx_fifo(1024),

m_rx_fifo(1024),

oscillator ("clk66",sc_time(15,SC_NS))

{

SC_CTHREAD(drive,clk.pos());

SC_THREAD(clkThread);

m_reg[ULPI_REG_VIDL] = 0x24;

m_reg[ULPI_REG_VIDH] = 0x04;

m_reg[ULPI_REG_PIDL] = 0x04;

m_reg[ULPI_REG_PIDH] = 0x00;

m_reg[ULPI_REG_FUNC] = 0x41;

m_reg[ULPI_REG_OTG] = 0x06;

m_reg[ULPI_REG_SCRATCH] = 0x00;

}

void clkThread(void)

{

while (true)

{

wait(oscillator.posedge_event());

clk.write (true);

wait(oscillator.negedge_event());

clk.write (false);

}

}

Semua. Pengeditan pertama selesai.

Membuat bus data dua arah

ULPI memiliki bus data dua arah. Dan dalam model kita melihat deskripsi berikut:

sc_out <sc_uint<8> > ulpi_data_o;

sc_in <sc_uint<8> > ulpi_data_i;

Kekacauan! Pertama kita akan membuat kosong berdasarkan bus keluaran, dan kemudian kita akan mengalihkan semuanya ke bus itu. Mulai dari mana? Dari fakta bahwa bus harus dapat masuk ke status ketiga, dan tipe sc_uint <8> hanya berfungsi dengan data biner. Jenis sc_lv <8> akan membantu kita . Oleh karena itu, kami mengubah deklarasi ban menjadi:

sc_inout <sc_lv<8> > ulpi_data_o;

Sekarang, masuklah ke file ulpi_driver.cpp dan cari semua panggilan ke bus ulpi_data_o di sana . Secara intuitif, saya menyadari bahwa hanya ada satu tempat untuk diperbaiki:

Teks yang sama.

void ulpi_driver::drive_input(void)

{

// Turnaround

ulpi_dir_o.write(false);

ulpi_nxt_o.write(false);

ulpi_data_o.write(0x00);

wait(oscillator.posedge_event());

}

Ubah baris yang dipilih menjadi

ulpi_data_o.write("ZZZZZZZZ");

Semua. Sekarang Anda dapat mengganti dua baris:

sc_inout <sc_lv<8> > ulpi_data_o;

sc_in <sc_uint<8> > ulpi_data_i;

tulis satu:

sc_inout <sc_lv<8> > ulpi_data;

dan mengganti semua referensi ke variabel lama baik di h-nick dan di cpp-shnik dengan referensi ke variabel ulpi_data .

Tambahkan alias port

Begitu. Setelah pencarian yang lama, saya sampai pada kesimpulan (mungkin salah) bahwa di lingkungan ModelSim mudah untuk mengambil dan melihat port untuk modul terpisah di SystemC menggunakan GUI, tidak berhasil. Namun, jika modul ini dimasukkan ke dalam sistem pengujian, modul tersebut akan muncul. Namun saat mengobrak-abrik teori tersebut, saya menemukan cara mengatur alias dengan indah untuk nama port. Konstruktor kelas terakhir sekarang terlihat seperti ini:

SC_HAS_PROCESS(ulpi_driver);

ulpi_driver(sc_module_name name): sc_module(name),

m_tx_fifo(1024),

m_rx_fifo(1024),

oscillator ("clk66",sc_time(15,SC_NS)),

rst_i ("rst"),

ulpi_data ("data"),

ulpi_dir_o ("dir"),

ulpi_nxt_o ("nxt"),

ulpi_stp_i ("stp")

{

SC_CTHREAD(drive,clk.pos());

SC_THREAD(clkThread);

m_reg[ULPI_REG_VIDL] = 0x24;

m_reg[ULPI_REG_VIDH] = 0x04;

m_reg[ULPI_REG_PIDL] = 0x04;

m_reg[ULPI_REG_PIDH] = 0x00;

m_reg[ULPI_REG_FUNC] = 0x41;

m_reg[ULPI_REG_OTG] = 0x06;

m_reg[ULPI_REG_SCRATCH] = 0x00;

}

Membuat sistem pengujian

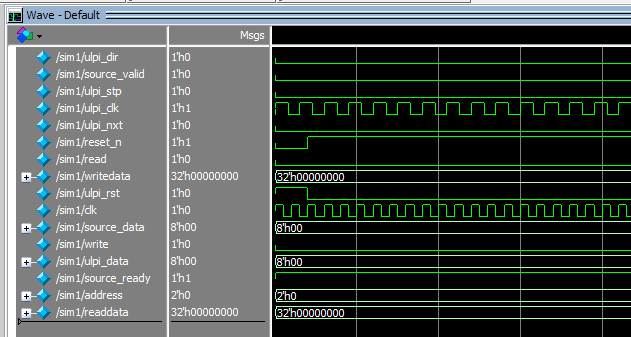

Baiklah kalau begitu. Saya tidak berhasil melakukan semuanya secara otomatis sehingga dua modul yang di-debug (kepala penganalisis dan model bus ULPI) melompat ke file pengujian itu sendiri. Tapi mari kita lakukan setidaknya tes awal, lalu tambahkan ULPI ke dalamnya. Menggunakan teknik dari artikel terakhir , saya membuat sistem pengujian untuk file ULPIhead.sv . Saya memiliki sebuah file yang bernama sim1.v dan segera menamainya sim1.sv .

Kemudian saya menambahkan modul ulpi_driver dengan pegangannya . Skrip yang dihasilkan myrun.do terlihat seperti ini:

vlog +../../SystemCPlay {../../MyCores/ULPIhead.sv}

sccom -g ../../SystemCPlay/ulpi_driver.cpp

sccom -link

vlog +../../SystemCPlay {../../SystemCPlay/sim1.sv}

vsim -voptargs="+acc" sim1

Baris terakhir disiksa. Tanpanya, kode Verilog tidak memiliki port. Dengan mengubah parameter pengoptimalan, kami menghilangkan masalah ini. Saya melihatnya di file * .do yang dibuat untuk mensimulasikan sistem kami di awal, ketika semuanya masih dilakukan di mesin. Benar, ada antrean panjang. Saya baru saja menemukan kunci yang memecahkan masalah dan menyalinnya. Dan - Saya tidak suka antrean panjang, saya membuang semua yang tidak perlu.

Sekarang kami menambahkan blok ULPI ke sistem pengujian dan membuat pengujian tiruan. Hanya untuk memastikan semua sinyal jam berdetak dan bus disetel ke nilai yang benar.

Saya mendapat tes ini.

Perhatikan teksnya.

`timescale 1ns / 1ns

module sim1 ;

reg ulpi_dir ;

wire source_valid ;

wire ulpi_stp ;

reg ulpi_clk ;

reg ulpi_nxt ;

reg reset_n ;

reg read ;

reg [31:0] writedata ;

wire ulpi_rst ;

reg clk ;

wire [7:0] source_data ;

reg write ;

wire [7:0] ulpi_data ;

reg source_ready ;

reg [1:0] address ;

wire [31:0] readdata ;

always

begin

clk = 1;

#5;

clk = 0;

#5;

end

ULPIhead DUT

(

.ulpi_dir (ulpi_dir ) ,

.source_valid (source_valid ) ,

.ulpi_stp (ulpi_stp ) ,

.ulpi_clk (ulpi_clk ) ,

.ulpi_nxt (ulpi_nxt ) ,

.reset_n (reset_n ) ,

.read (read ) ,

.writedata (writedata ) ,

.ulpi_rst (ulpi_rst ) ,

.clk (clk ) ,

.source_data (source_data ) ,

.write (write ) ,

.ulpi_data (ulpi_data ) ,

.source_ready (source_ready ) ,

.address (address ) ,

.readdata (readdata ) );

ulpi_driver ULPI

(

.clk (ulpi_clk),

.rst (ulpi_rst),

.data (ulpi_data),

.dir (ulpi_dir),

.nxt (ulpi_nxt),

.stp (ulpi_stp)

);

initial

begin

reset_n = 1'b0;

source_ready = 1;

writedata = 0;

address = 0;

read = 0;

write = 0;

#20

reset_n = 1'b1;

end

endmodule

Kesimpulan

Setidaknya, kami telah menguasai pemodelan dalam bahasa SystemC menggunakan sistem ModelSim. Namun, ternyata ini membutuhkan akses ke versi 32-bit berlisensi. Versi gratis dan versi 64-bit berlisensi tidak memberikan kesempatan seperti itu. Seperti yang saya pahami, semuanya dapat dilakukan secara gratis di sistem Icarus Verilog, tetapi saya tidak tahu persis bagaimana mencapainya. Ternyata lebih mudah bagi saya untuk mengakses ModelSim yang diperlukan. Di artikel berikutnya, kita akan menggunakan pengetahuan ini untuk menjadi model kepala kita.

Selama pekerjaan, modifikasi model yang cukup kompleks dibuat. File yang dihasilkan dapat diunduh di sini .