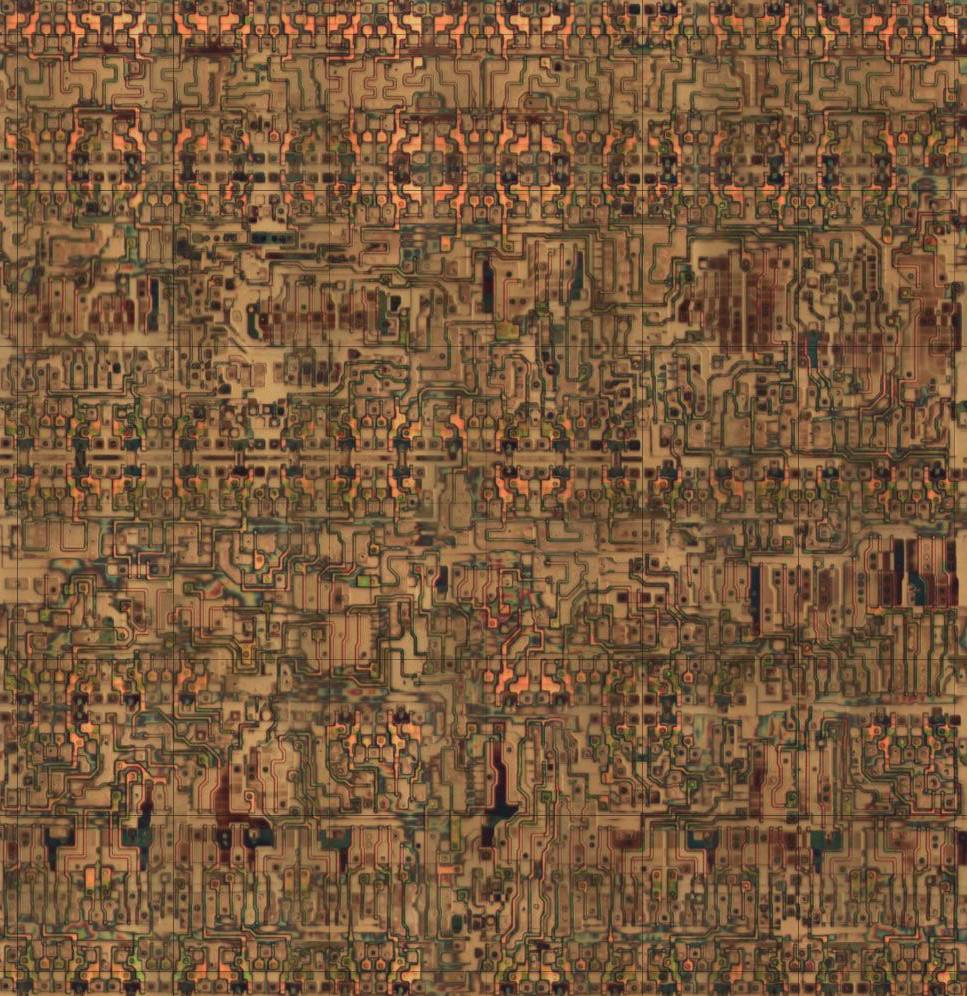

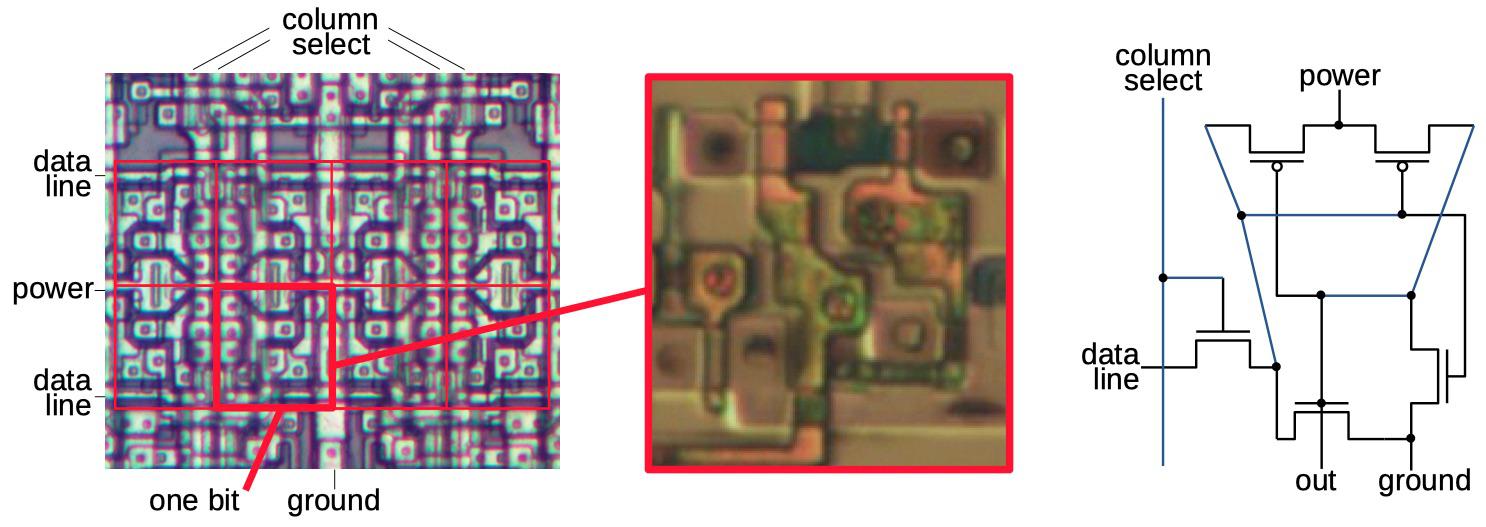

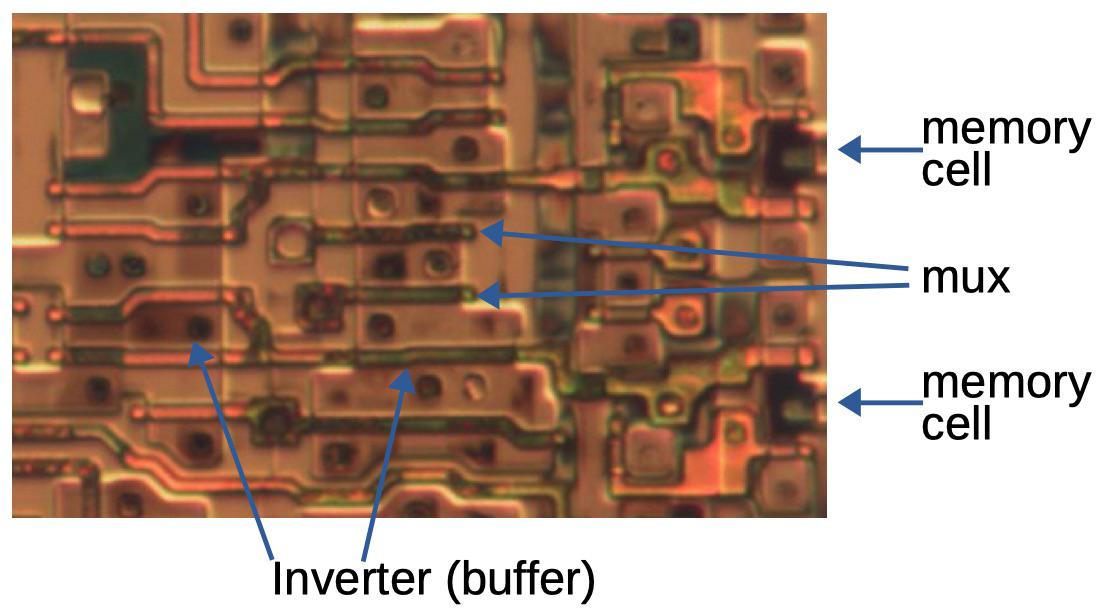

Foto itu menunjukkan salah satu dari 64 blok chip XC2064. Lapisan metalisasi dihilangkan, kita dapat melihat transistor silikon dan polysilicon tergeletak di bawah metalisasi. Anda dapat melihat foto berskala lebih besar di sini: siliconpr0n .

FPGA ditemukan oleh Ross Freeman, salah satu pendiri Xilinx pada tahun 1984, FPGA pertama adalah XC2064. Itu jauh lebih sederhana daripada FPGA modern, hanya berisi 64 blok logika, dibandingkan dengan ribuan dan jutaan dalam FPGA modern, dan pembuatannya menyebabkan munculnya industri bernilai miliaran dolar. XC2064 sangat penting sehingga masuk ke Chips Hall of Fame. Saya telah merekayasa balik XC2064 dan dalam posting ini saya menjelaskan struktur internalnya secara umum dan bagaimana ia diprogram dengan bitstream.

Xilinx

Xilinx -. , , Xilinx , . Xilinx Seiko Epson Semiconductor Division ( Seiko Epson).

XC2064

: ( ) . — (Programmable Logic Devices, PLD), , , 1967 . , , , . , PROM, , , EPROM, . , , Programmable Logic Array, Programmable Array Logic (1978), Generic Array Logic Uncommitted Logic Array. , , « », . , , , , , . , . "Three Ages of FPGAs: A Retrospective on the First Thirty Years of FPGA Technology." "A Brief History of FPGAs".

Xilinx XC2064 adalah chip FPGA pertama. Diambil dari sini: siliconpr0n .

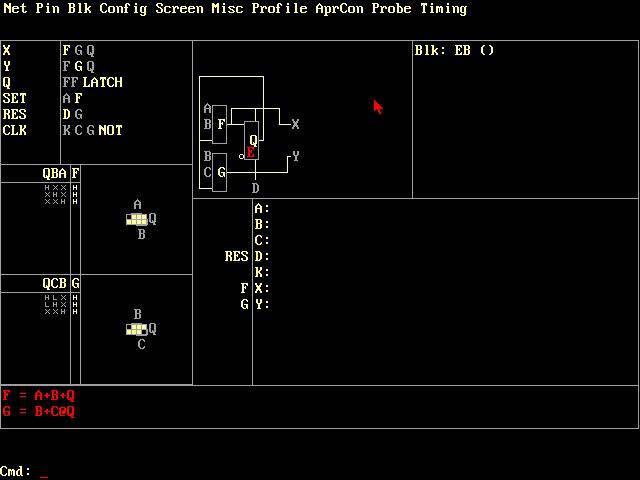

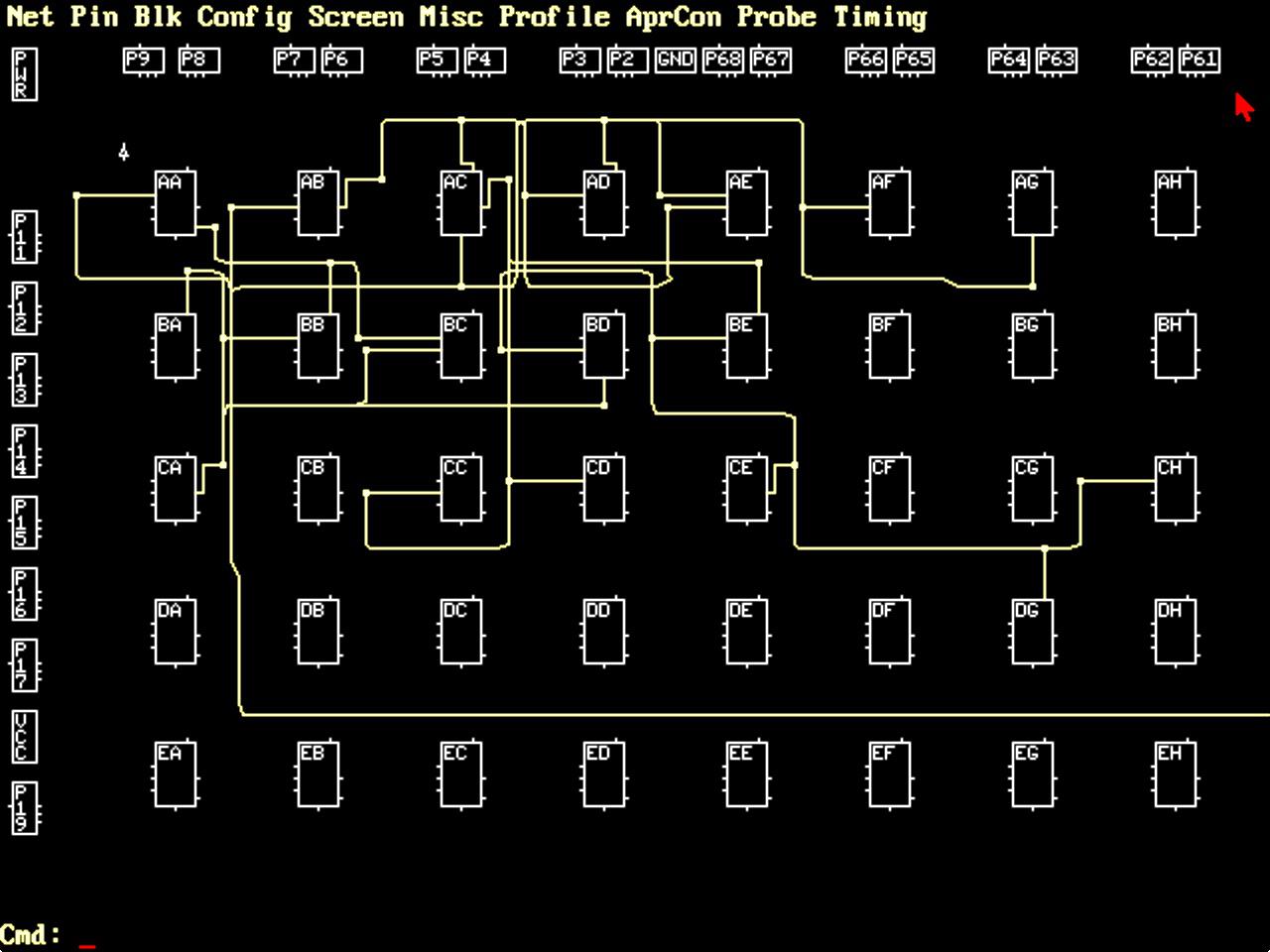

FPGA saat ini diprogram dalam bahasa deskripsi perangkat keras seperti Verilog atau VHDL, tetapi pada saat itu, Xilinx menyediakan perangkat lunak pengembangannya sendiri, aplikasi MS-DOS yang disebut XACT, dengan harga $ 12.000. XACT bekerja pada tingkat yang lebih rendah daripada alat modern: pengguna menentukan fungsi setiap blok logis, seperti yang ditunjukkan pada gambar di bawah, dan koneksi antara blok logis.

XACT merutekan koneksi dan menghasilkan file konfigurasi (bitstream) yang dimuat ke dalam FPGA.

Tangkapan layar dari XACT. Kedua tabel F dan G menerapkan persamaan yang ditunjukkan di bagian bawah layar, dengan peta Karnaugh ditunjukkan di atas.

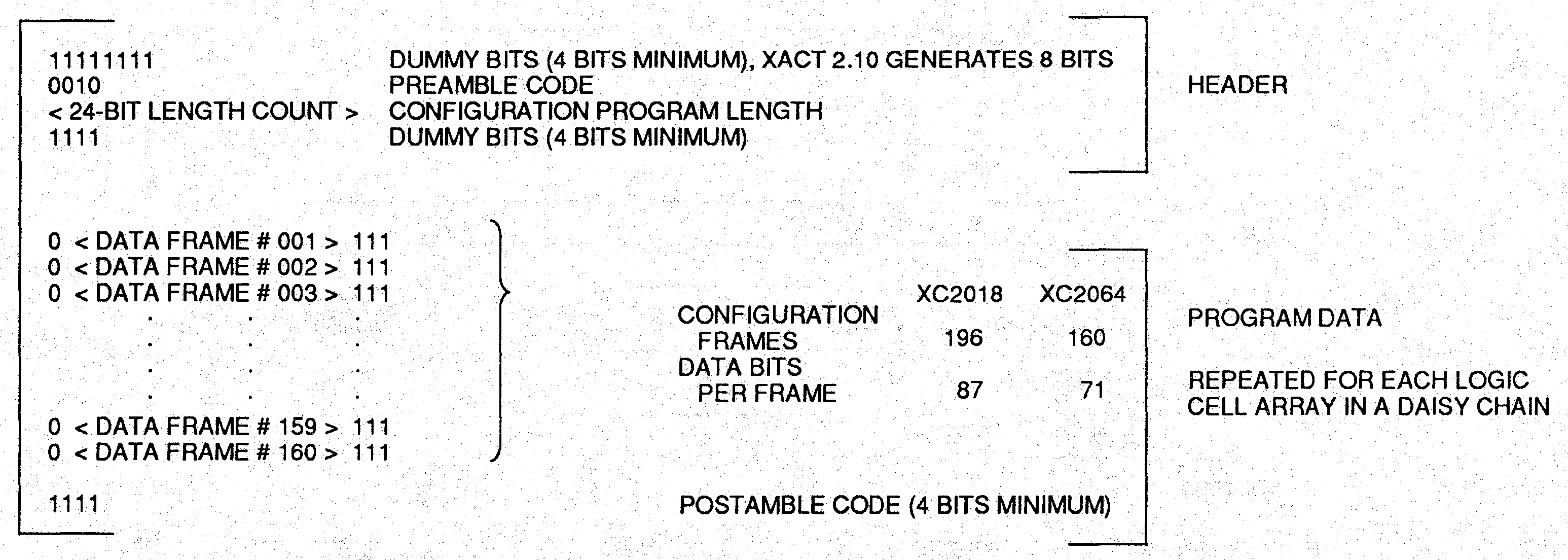

FPGA dikonfigurasi menggunakan bitstream, urutan bit dalam format berpemilik. Jika Anda melihat bitstream XC2064 (di bawah), Anda akan melihat campuran pola misterius yang berulang secara tidak teratur dan tersebar di seluruh bitstream. Namun, mempelajari sirkuit fisik dari FPGA mengungkapkan struktur data bitstream dan dapat dipelajari.

Bagian dari bitstream yang dihasilkan oleh XACT.

Bagaimana cara kerja FPGA?

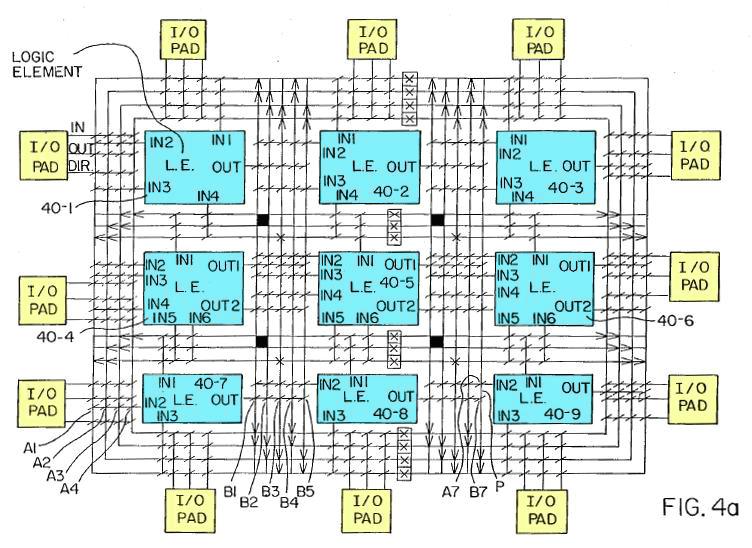

Gambar di bawah ini, diambil dari paten FPGA asli, menunjukkan struktur dasar sebuah FPGA. FPGA yang disederhanakan ini memiliki total 9 blok logika (ditandai dengan warna biru), dan 12 port I / O. Jaringan interkoneksi menghubungkan komponen bersama. Dengan mengatur sakelar (garis diagonal) pada koneksi, blok logika dapat dihubungkan satu sama lain dan ke port I / O. Setiap elemen logika dapat diprogram untuk fungsi logika yang diperlukan. Akibatnya, chip yang dapat diprogram seperti itu dapat mengimplementasikan perangkat apa pun yang sesuai dengan ruang yang tersedia.

Paten FPGA , blok logis (LE) saling berhubungan.

Blok Logika yang Dapat Dikonfigurasi (CLB)

Meskipun gambar di atas menunjukkan 9 CLB, XC2064 memiliki 64 CLB. Gambar di bawah ini menunjukkan struktur CLB. CLB memiliki 4 input (A, B, C, D) dan dua output (X dan Y). Di antaranya adalah logika kombinasional, yang dapat diprogram ke fungsi logika apa pun yang diinginkan. CLB juga berisi pemicu, yang keberadaannya memungkinkan Anda untuk mengimplementasikan penghitung, register geser, mesin status, dan sirkuit stateful lainnya. Trapesium menunjukkan multiplexer yang dapat diprogram untuk melewatkan sinyal dari salah satu input. Multiplexer memungkinkan Anda untuk mengkonfigurasi CLB untuk tugas tertentu dengan memilih sinyal tertentu untuk mengontrol pemicu dan keluaran.

Blok logika yang dapat dikonfigurasi di XC2064, diambil dari sini: lembar data .

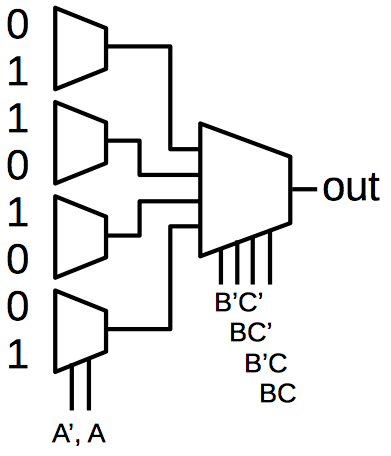

Anda mungkin bertanya-tanya bagaimana logika kombinasional mengimplementasikan fungsi logika arbitrer. Apakah ada pilihan antara kumpulan AND, OR, XOR, dan seterusnya? Tidak, ada trik rapi yang disebut tabel pencarian (LUT), yang sebenarnya merupakan tabel kebenaran untuk suatu fungsi. Misalnya, fungsi dari tiga variabel ditentukan oleh tabel yang terdiri dari 8 baris. LUT berisi 8 bit memori. Kita dapat mengimplementasikan fungsi logika 3-input sembari mempertahankan ketiga bit tersebut.

Lihat tabel

XC2064 — , . CLB . XC2064 , 4 . , .

XC2064 . .

XC2064 . .

Koneksi

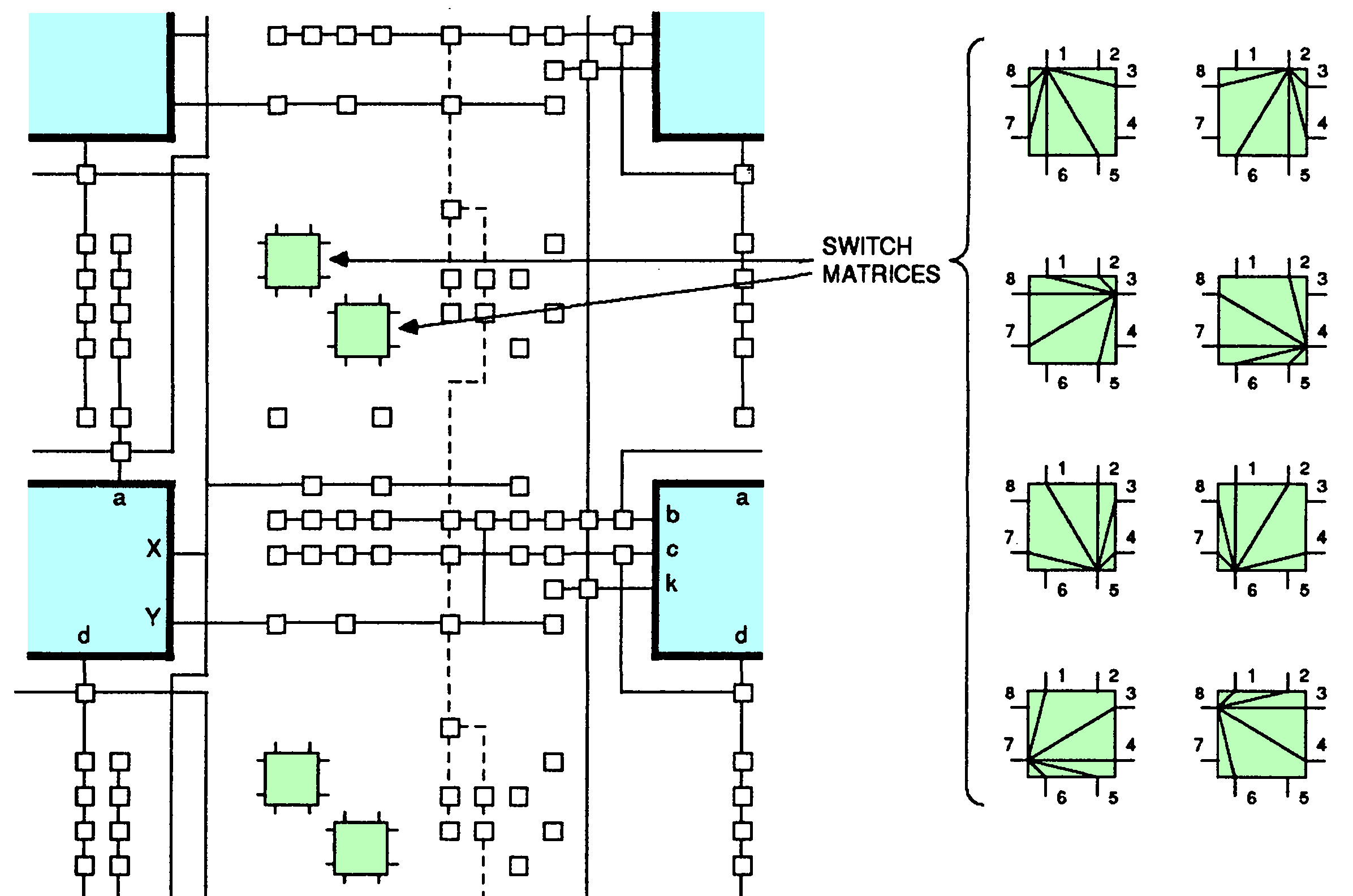

Aspek kunci berikutnya dari FPGA adalah koneksi, yang dapat diprogram untuk mengganti CLB dengan berbagai cara. Hubungannya rumit, tetapi gambaran kasarnya adalah bahwa ada segmen sambungan vertikal dan horizontal antara semua CLB. Anda dapat menghubungkan CLB dengan garis horizontal dan vertikal, dan membuat koneksi arbitrer. Jenis koneksi yang lebih kompleks adalah "matriks sakelar". Setiap matriks memiliki 8 pin yang dapat dihubungkan satu sama lain (hampir) dengan cara apa pun.

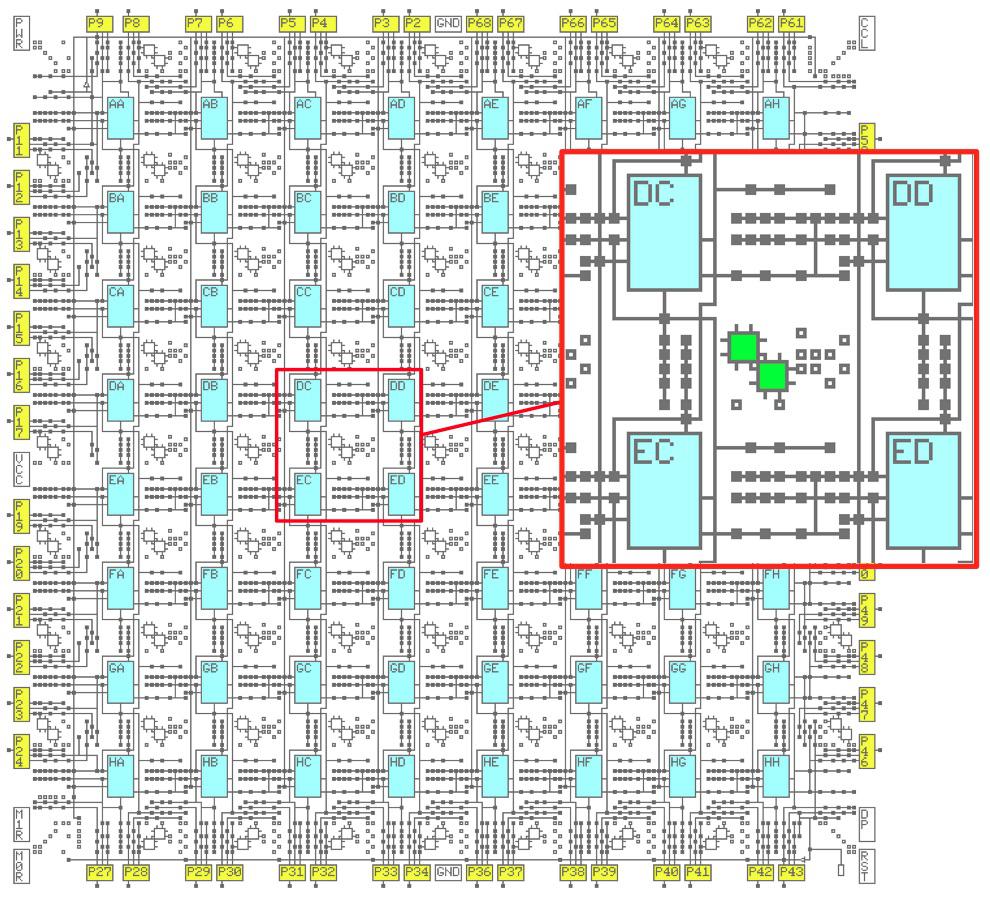

Gambar di bawah ini menunjukkan struktur link XC2064 yang menyediakan koneksi antara blok logika (biru) dan garis I / O (kuning). Sisipan menunjukkan detail mekanisme kopling. Persegi panjang hijau adalah matriks sakelar 8-pin dan kotak kecil adalah titik koneksi yang dapat diprogram.

FPGA XC2064 memiliki matriks CLB 8x8. Setiap CLB memiliki nama dari AA hingga HH.

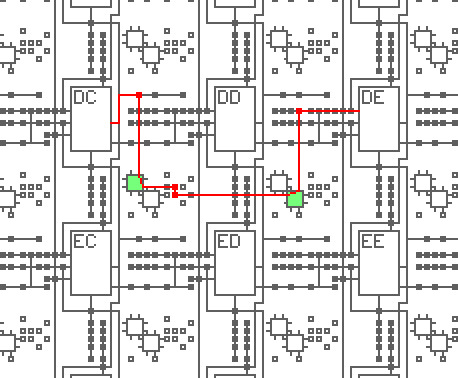

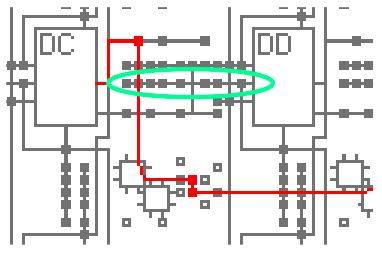

Sambungan dapat mengalihkan, misalnya, keluaran dari blok DC ke masukan dari blok DE, seperti yang ditunjukkan di bawah ini. Garis merah menunjukkan jalur sinyal dan kotak merah kecil menunjukkan titik koneksi yang diaktifkan. Keluar dari blok DC, sinyal dialihkan ke titik koneksi pertama pada sakelar 8-pin (hijau), yang merutekannya melalui dua titik koneksi dan sakelar 8 arah lainnya (garis vertikal dan horizontal yang tidak digunakan tidak ditampilkan). Perhatikan bahwa koneksi cukup kompleks, bahkan jalur pendek seperti itu menggunakan empat titik koneksi dan dua sakelar.

Contoh perutean sinyal dari output blok DC ke blok DE.

Tangkapan layar di bawah ini menunjukkan bagaimana pelacakan dilakukan di XACT. Garis kuning menunjukkan hubungan antara blok logika. Dengan bertambahnya jumlah sinyal, menjadi sulit untuk membuat koneksi tanpa konflik antar jalur. XACT secara otomatis melacak, tetapi jejak juga dapat diedit secara manual.

Tangkapan layar program XACT. Ini adalah program MS-DOS dan dikendalikan oleh keyboard dan mouse.

Penerapan

Selanjutnya, kita akan melihat sirkuit internal XC2064 dengan rekayasa balik dari foto kristal. Berhati-hatilah karena hal ini memerlukan pemahaman dengan XC2064.

Foto kristal

XC2064 XC20186, XC2064 XC2018 siliconpr0n. , . John McMaster , , . , .

XC2064 , John McMaster.

XC2064 , John McMaster.

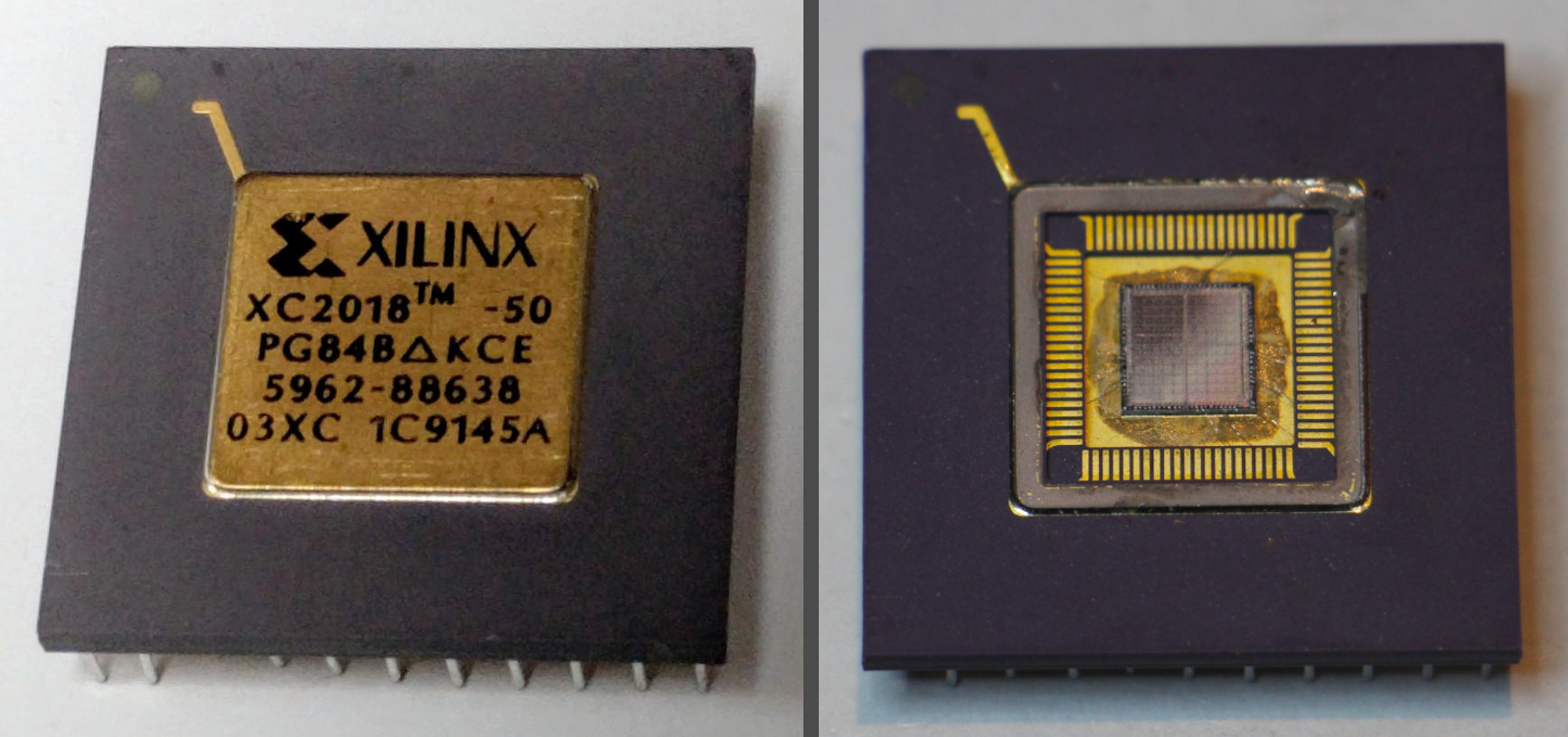

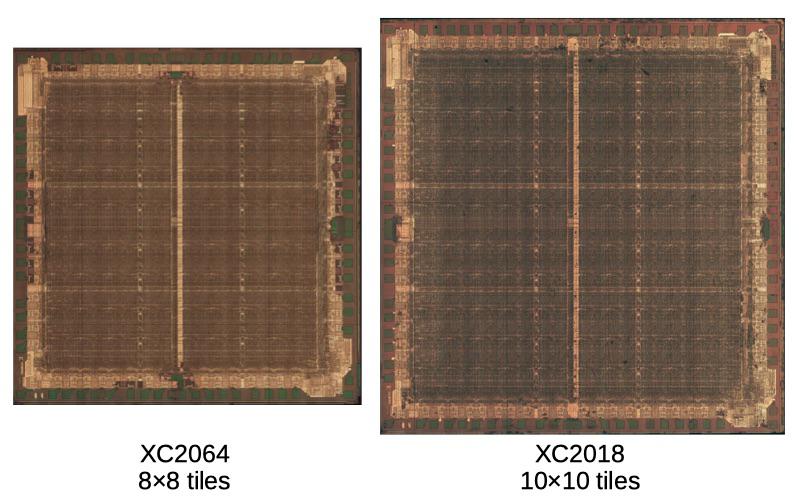

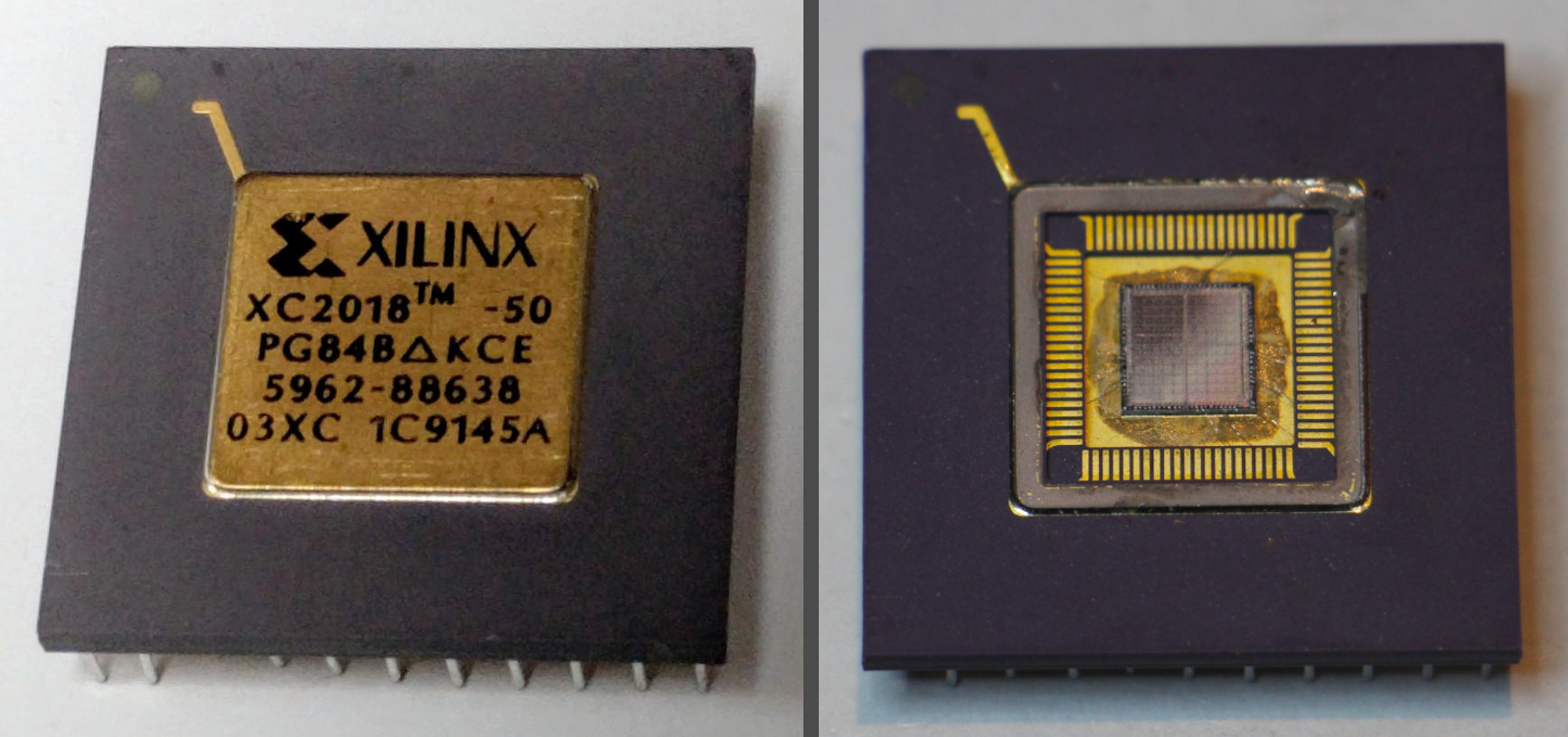

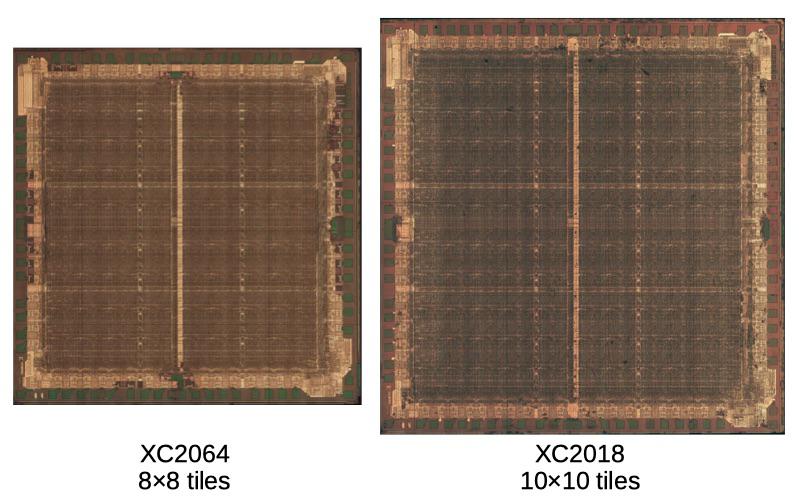

XC2018

Xilinx XC2018 ( ) 100 , , XC2064. , XC2064 64 , 1010, 88. XC2018 , .

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

XC2018. , . .

XC2064 XC2018. , , .

XC2064 XC2018. , , , . siliconpr0n.

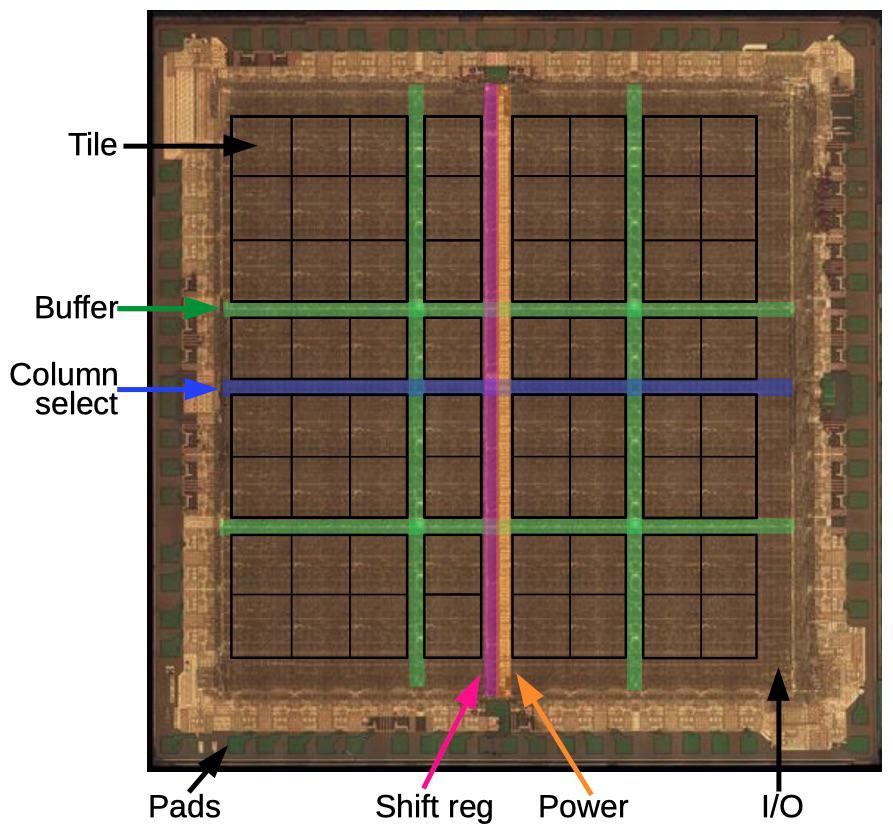

Di bawah ini adalah foto kristal XC2064. Bagian utama dari FPGA adalah matriks blok 8x8, yang masing-masing berisi blok logika dan sirkuit sekitarnya. Meskipun diagram FPGA menunjukkan blok logis (CLB) sebagai terpisah dari diagram pengkabelan entitas, pada kenyataannya tidak demikian. Faktanya, setiap blok logika dan lingkungannya diimplementasikan sebagai simpul tunggal, ubin. (Tepatnya, ubin menyertakan koneksi di bagian atas dan kiri setiap CLB.)

Blok tata letak pada chip XC2064. Diambil dari sini: siliconpr0n .

Terletak di sepanjang sisi sirkuit terintegrasi, blok I / O menyediakan komunikasi dengan dunia luar. Mereka terhubung ke pin kristal, yang ditampilkan sebagai kotak hijau kecil, dan terhubung ke pin casing sirkuit mikro. Ada buffer pada dadu (hijau): dua vertikal dan dua horizontal. Buffer ini memperkuat sinyal yang menempuh jarak jauh melintasi chip dan mengurangi latensi. Register geser vertikal (merah muda) dan rantai pengambilan kolom horizontal digunakan untuk memuat aliran bit ke dalam chip, seperti yang ditunjukkan di bawah ini.

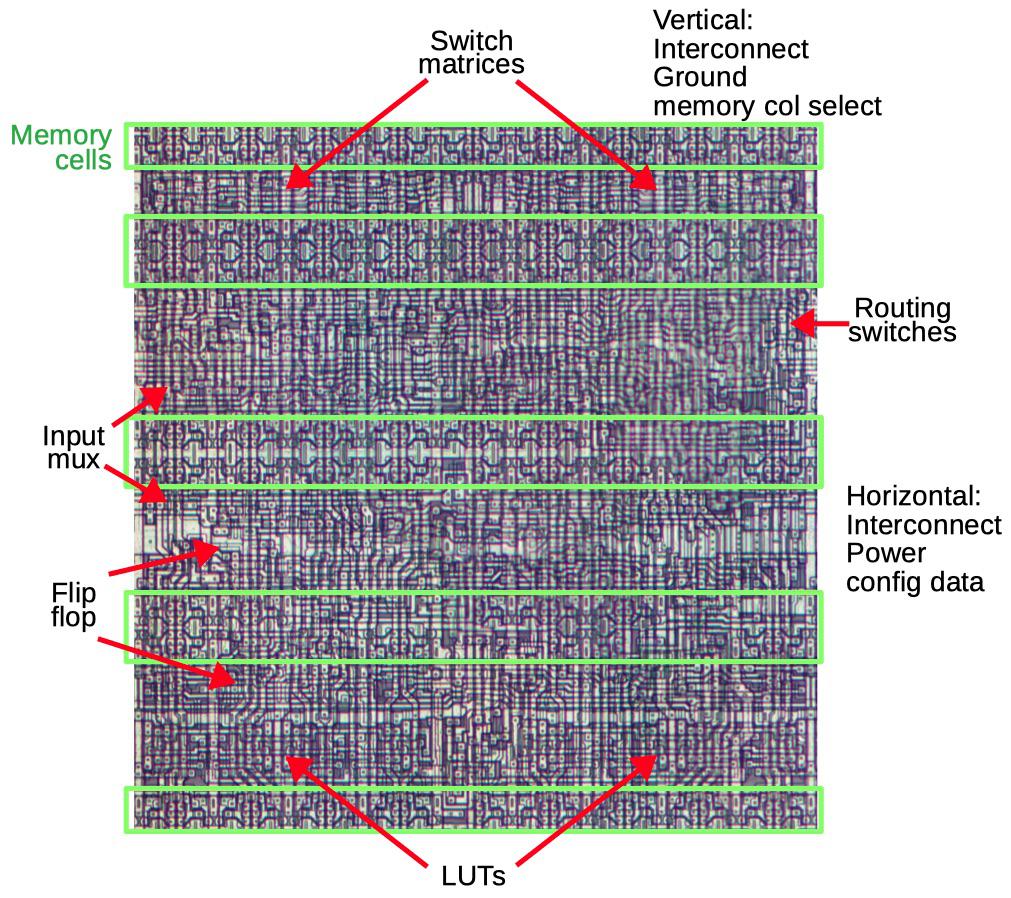

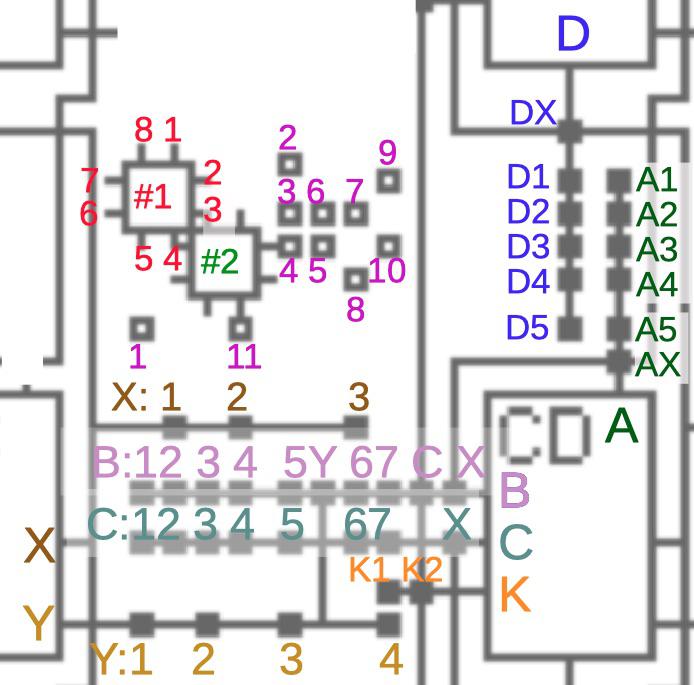

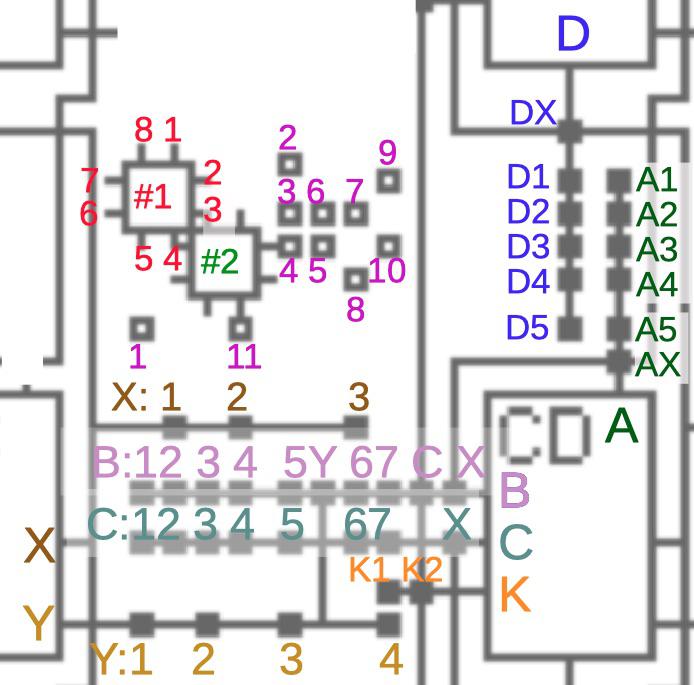

Di dalam ubin

Gambar di bawah ini menunjukkan struktur satu ubin XC2064, chip berisi 64 ubin semacam itu yang dikemas dalam satu cetakan. Sekitar 40% dari setiap ubin ditempati oleh sel memori (ditampilkan dalam warna hijau) yang menyimpan bit konfigurasi. Sepertiga atas (kurang-lebih) ubin berisi diagram koneksi: dua matriks sakelar dan sejumlah sakelar tautan individual. Di bawah ini adalah blok logika. Bagian utama dari blok logika adalah multiplexer input, flip-flop, dan tabel pencarian. Ubin terhubung ke tetangga melalui jalur komunikasi horizontal dan vertikal, dan juga terhubung ke rel listrik dan arde. Bit data konfigurasi memasuki sel memori secara horizontal, dan sinyal vertikal memilih kolom tertentu untuk dimuat.

Satu ubin FPGA menunjukkan node fungsional penting

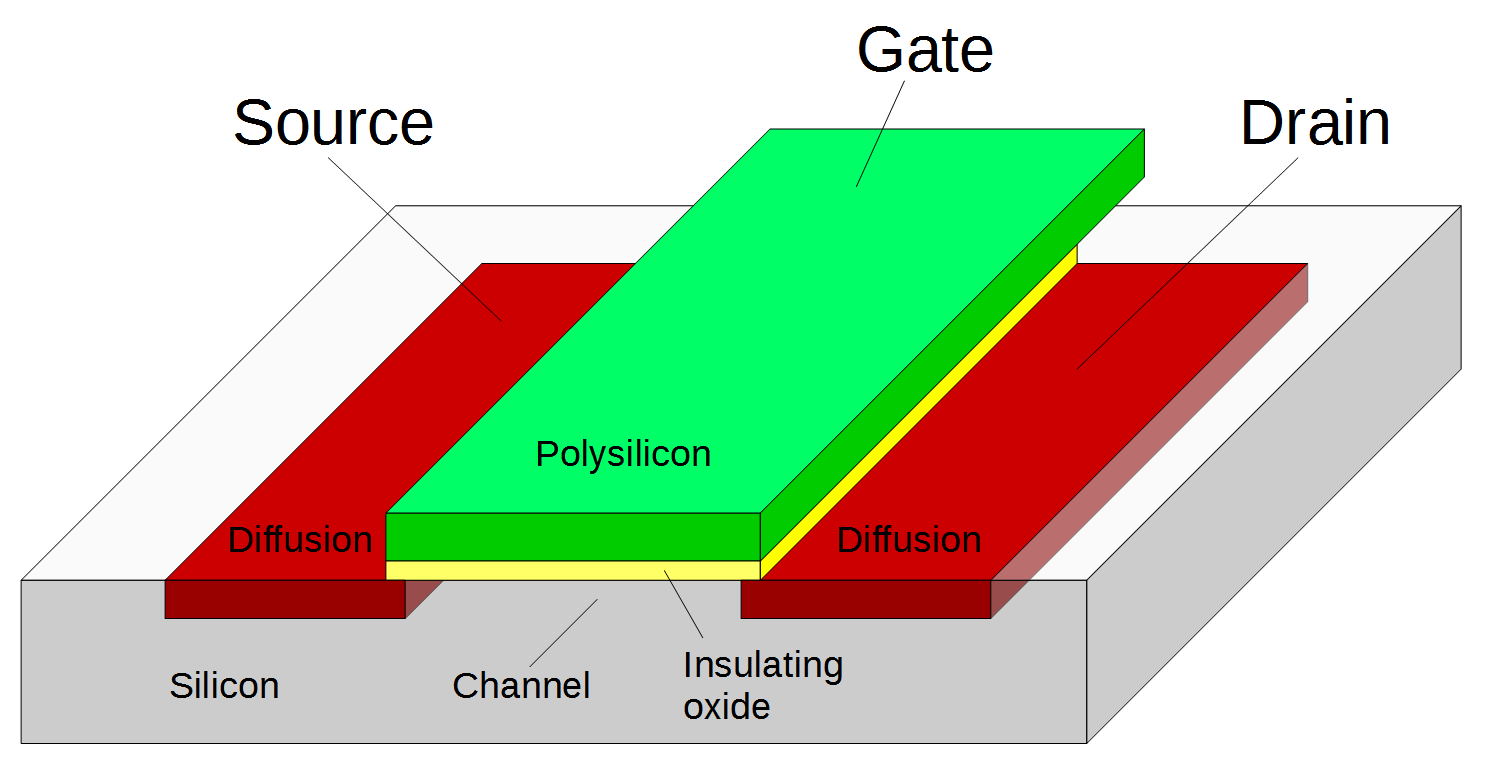

Transistor

FPGA diimplementasikan pada logika CMOS (CMOS), dibangun dari transistor NMOS dan PMOS. Transistor memainkan dua peran utama dalam FPGA. Pertama, unsur logika dibentuk dari kombinasinya. Kedua, transistor digunakan sebagai sakelar yang dilewati sinyal, misalnya, untuk membentuk koneksi antar blok. Transistor yang melakukan peran ini disebut transistor tembus. Gambar di bawah ini menunjukkan struktur dasar MOSFET. Dua bagian silikon diolah dengan kotoran untuk membuat saluran pembuangan dan sumber. Di antara mereka ada gerbang yang menghidupkan dan mematikan transistor dan mengontrol arus antara drain dan sumber. Penutupnya terbuat dari jenis silikon khusus yang disebut polysilicon, diisolasi dari silikon di bawahnya oleh lapisan tipis oksida. Di atasnya, ada dua lapisan metalisasi, yang menyediakan koneksi sirkuit.

Struktur MOSFET

Dalam foto kristal, kita dapat mengamati seperti apa transistor itu di bawah mikroskop. Gerbang polysilicon adalah garis berkelok-kelok antara dua wilayah silikon yang diolah. Lingkaran-lingkaran tersebut menghubungkan silikon dan lapisan logam (yang dihilangkan dalam foto ini).

MOSFET FPGA

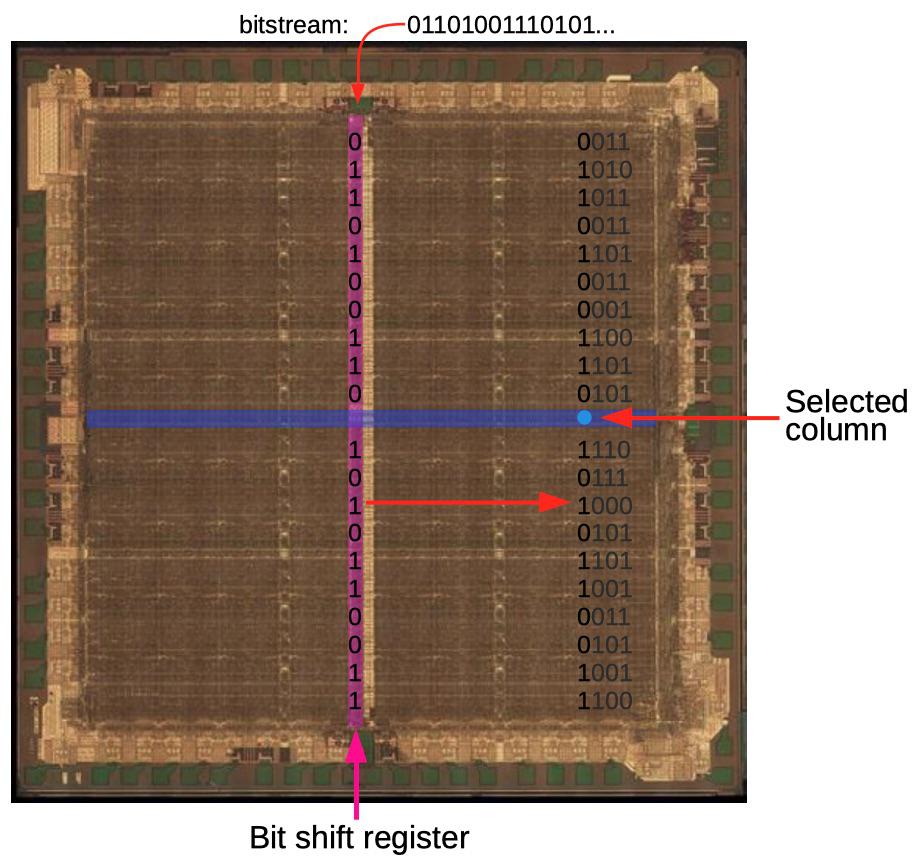

Bitstream dan memori konfigurasi

Informasi konfigurasi di XC2064 disimpan di lokasi memori konfigurasi. FPGA tidak menggunakan memori blok untuk ini, sebaliknya, memori konfigurasi didistribusikan ke seluruh kristal dalam bentuk kisi 160x71, setiap bit ditempatkan di sebelah sirkuit yang dikontrolnya. Gambar di bawah ini menunjukkan konfigurasi bitstream yang dimuat ke dalam FPGA. Bitstream dimuat ke register geser yang berada di tengah chip (merah muda). Setelah 71 bit dimuat ke dalam register geser, rangkaian pengambilan kolom (biru) memilih kolom memori yang diinginkan dan bit tersebut dimuat ke dalam kolom secara paralel. Kemudian 71 bit berikutnya dimuat ke register geser dan kolom berikutnya di sebelah kiri dipilih. Proses ini diulangi untuk 160 kolom FPGA, dan seluruh bitstream dimuat ke dalam FPGA. Penggunaan register geser menghilangkan kebutuhan akan sirkuit pengalamatan memori yang besar.

Bagaimana bitstream dimuat ke dalam FPGA. Bit ditunjukkan secara konvensional, penyimpanan bit sebenarnya jauh lebih padat. Tiga kolom di sebelah kanan telah dimuat dan kolom keempat sedang dimuat. Foto kristal diambil dari sini: siliconpr0n .

Hal yang penting adalah bahwa aliran bit didistribusikan ke seluruh chip persis dengan urutan bit muncul di file: pengemasan bit dalam bitstream sesuai dengan penempatan fisiknya pada chip. Seperti yang ditunjukkan di bawah ini, setiap bit disimpan dalam FPGA di sebelah sirkuit yang dikontrolnya. dengan demikian, format file bitstream secara langsung ditentukan oleh penempatan sirkuit perangkat keras. Misalnya, jika ada celah di antara petak, dan ada penyangga di dalamnya, celah yang sama akan berada di aliran bit. Struktur bitstream tidak bergantung pada abstraksi perangkat lunak seperti bidang dalam tabel data atau blok konfigurasi. Memahami bitstream membutuhkan pemikiran dalam istilah perangkat keras, bukan perangkat lunak

Bitstream

, (.RBT) , .

, .

, .

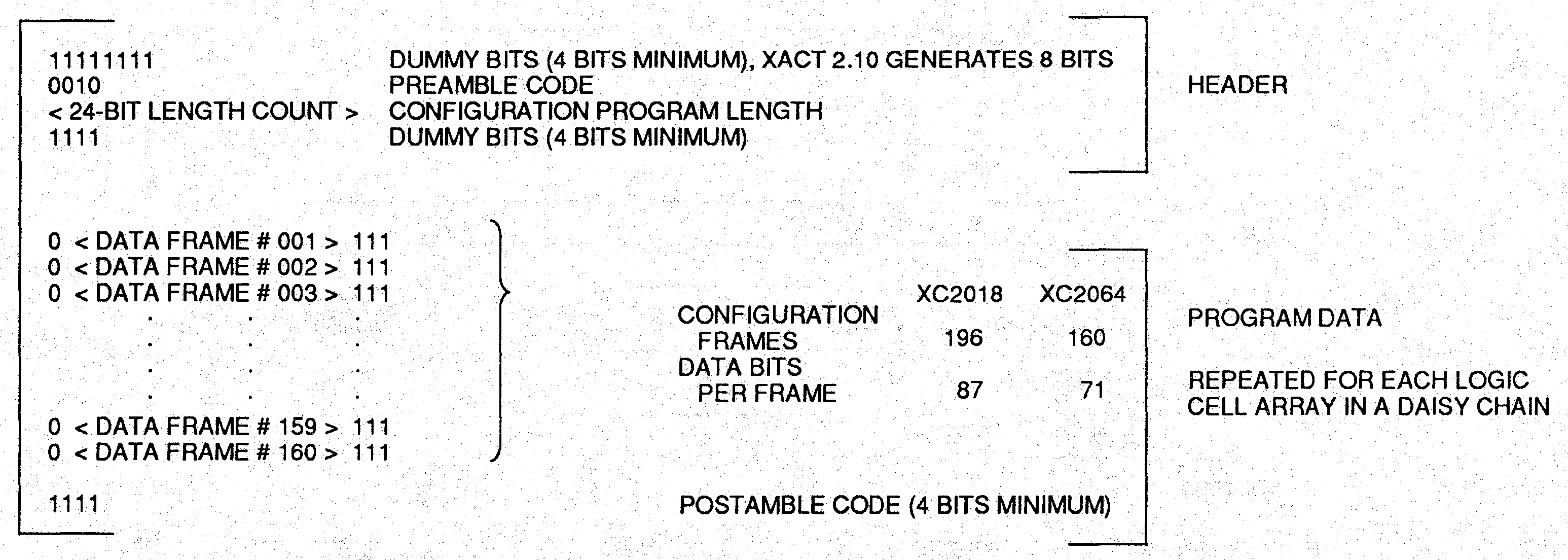

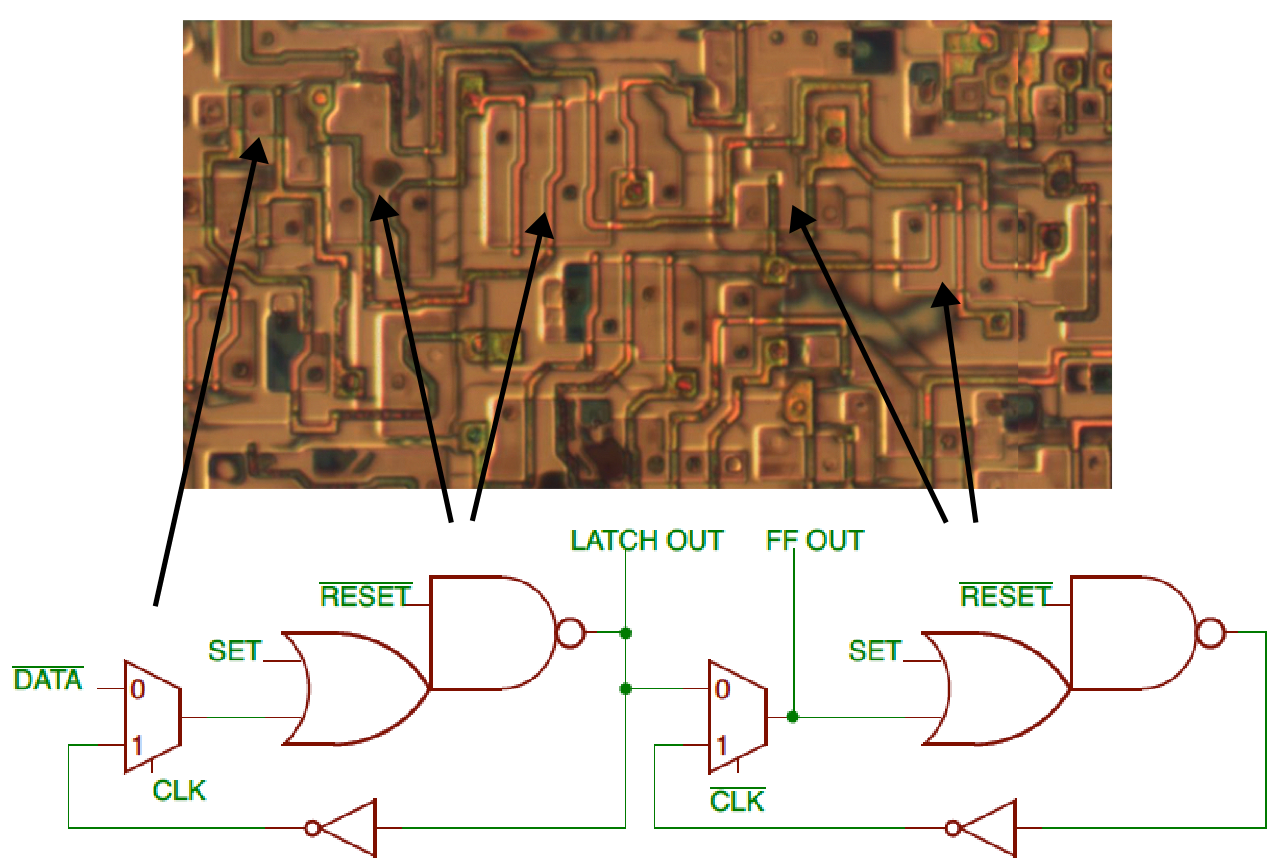

Setiap bit memori konfigurasi diimplementasikan seperti yang ditunjukkan di bawah ini. Setiap sel memori terdiri dari dua inverter yang terhubung dalam satu lingkaran. rangkaian seperti itu memiliki dua kondisi stabil, dan dapat menyimpan satu bit: inverter atas dalam kondisi 1, dan inverter bawah dalam kondisi 0, atau sebaliknya. Untuk menulis ke sel, transistor pass di sebelah kiri diaktifkan, melewatkan sinyal. Sinyal pada jalur data hanya menarik inverter, menulis bit yang diperlukan. (Anda juga dapat membaca data konfigurasi menggunakan rung yang sama.) Output Q dan Q terbalik mengontrol fungsi tertentu di FPGA, seperti menutup interkoneksi, mengambil sedikit dari tabel pencarian, atau mengontrol pemicu. Dalam kebanyakan kasus, hanya keluaran Q yang digunakan.

Sel SRAM

(SRAM). , RAM, , , SRAM. , 5T SRAM.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

, . , . , 1818 , 27 . , , , , . 9 .

, , . siliconpr0n.

Diagram satu bit memori konfigurasi, dari dokumentasi.

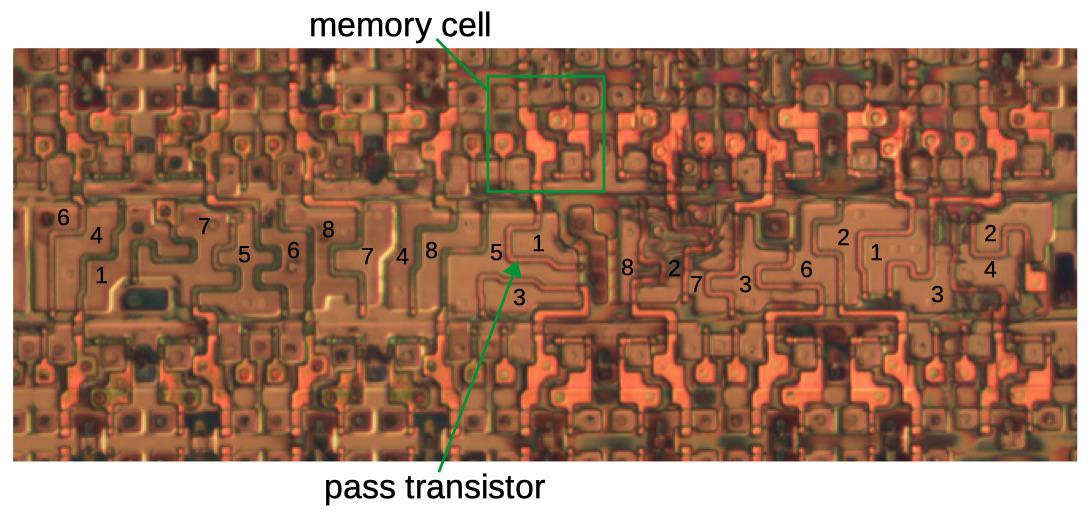

Gambar di bawah ini menunjukkan struktur fisik sel memori. Foto di sebelah kiri menunjukkan 8 sel memori, salah satunya disorot. Setiap baris data horizontal terhubung ke semua lokasi memori di baris tersebut. Setiap baris pengambilan kolom memilih semua lokasi memori di kolom, memungkinkan penulisan. Foto tengah menunjukkan bagian silikon dan polisilikon untuk satu sel memori. Lapisan logam telah dihilangkan untuk mengekspos transistor di bawahnya. Lapisan metalisasi menghubungkan transistor, lingkaran di foto, ini adalah sambungan, vias, antara silikon atau polisilikon dan logam. Diagram menunjukkan bagaimana lima transistor terhubung, penempatan elemen pada diagram sesuai dengan penempatannya di foto. Dua pasang transistor membentuk CMOS inverter, dengan transistor pass-through di kiri bawah menyediakan akses ke sel.

, . — . , . . : siliconpr0n.

Seperti yang dijelaskan sebelumnya, FPGA mengimplementasikan fungsi logika arbitrer menggunakan tabel pencarian. Gambar di bawah ini menunjukkan bagaimana tabel pencarian diimplementasikan di XC2064. Delapan nilai di sebelah kiri disimpan di delapan lokasi memori. Empat multiplexer memilih satu dari setiap pasangan nilai, tergantung pada nilai pada input A, jika A = 0, nilai atas dipilih, jika A = 1, maka semakin rendah. Kemudian, multiplexer besar memilih satu dari empat nilai berdasarkan sinyal B dan C. Hasilnya adalah nilai tertentu, dalam hal ini A XOR B XOR C. Kita dapat melakukan fungsi logika apa pun jika kita mengganti nilai yang berbeda ke dalam tabel.

Implementasi XOR di tabel pencarian.

Setiap multiplexer diimplementasikan dengan transistor pass-through. Bergantung pada sinyal kontrol, salah satu transistor pass-through diaktifkan, meneruskan data dari input ke output. Gambar di bawah ini menunjukkan sebagian dari rantai LUT, dengan dua bit multiplexing. Di sebelah kanan ada dua lokasi memori. Setiap bit melewati inverter, diperkuat, dan melewati transistor pass-through dari multiplexer di tengah, memilih salah satu bit ini.

Tampilan jaring yang menerapkan LUT. Diambil dari siliconpr0n.

Pelatuk

Setiap CLB berisi flip-flop yang memungkinkan FPGA untuk mengimplementasikan latch, mesin status, dan jaring stateful lainnya. Gambar di bawah ini menunjukkan implementasi pemicu (agak tidak biasa). Dia menggunakan skema berikut. Ketika sinyal clock nol, mux pertama meneruskan data ke kait pertama, yang menyimpan nilainya. Bit dibalik dua kali saat melewati gerbang OR, NAND dan inverter dan hasilnya tetap sama. selanjutnya, multiplexer kait kedua menerima bit dari kait pertama ketika jam naik ke 1 (perhatikan bahwa jam terbalik). Nilai ini merupakan keluaran dari flip-flop. Ketika sinyal clock diatur ke 0, multiplexer sekunder menutup loop dengan mengunci bit. Jadi, pelatuknya sensitif terhadap tepi sinyal,mengunci nilai di tepi depan sinyal clock. Setel dan setel ulang garis set dan setel ulang flip-flop

. OR-NAND : siliconpr0n.

Matriks sakelar merupakan elemen interkoneksi yang penting. Setiap sakelar memiliki 8 pin (dua di setiap sisi) dan dapat menghubungkannya dengan hampir semua cara. Sinyal dapat dibuka, dipisahkan, berpotongan dengan lebih fleksibel daripada di node interkoneksi individu. Gambar di bawah ini menunjukkan sebagian jaringan interkoneksi antara keempat CLB (biru). Matriks switching (hijau) dapat dihubungkan dengan kombinasi koneksi apa pun di sisi kanan. Perhatikan bahwa setiap pin dapat dihubungkan ke pin lainnya sebanyak 5 hingga 7 buah. Misalnya, pin 1 dapat dihubungkan ke pin 3, tetapi tidak ke pin 2 dan 4. Hal ini membuat matriks hampir lengkap, dengan 20 kemungkinan koneksi, bukan 28.

Diambil dari sini: Buku Data Array Gerbang yang Dapat Diprogram Xilinx , gbr. 7b.

Matriks switching dibentuk oleh deretan transistor pass-through yang dikendalikan oleh sel memori di atas dan di bawahnya. Kedua sisi transistor merupakan dua pin dari switching matrix yang dapat dihubungkan oleh transistor. Jadi setiap matriks memiliki 20 bit kontrol, dua matriks per ubin memberi kita 40 bit per ubin. Foto di bawah ini menunjukkan satu sel memori yang terhubung ke gerbang bergelombang transistor lulus di bawahnya. Transistor ini menyediakan koneksi antara pin 5 dan pin 1. Jadi, bit dalam bitstream yang sesuai dengan lokasi memori ini mengontrol koneksi antara pin 5 dan 1. Demikian pula, sel memori lain dan transistor terkait mengontrol koneksi lain. Perhatikan juga bahwa urutan koneksi ini tidak mengikuti pola tertentu, sebagai hasilnya,korespondensi antara bit di bitstream dan pin sakelar terlihat acak.

Ganti Matriks

20 . 18 , .

Penerapan matriks koneksi 8-lead. Daerah silikon ditentukan oleh nomor pin yang sesuai. Lapisan logam yang menghubungkan kabel yang sesuai ke transistor telah dihilangkan. Diambil dari siliconpr0n.

Koneksi input

Input CLB menggunakan skema encoding bitstream yang berbeda, yang dijelaskan oleh implementasi perangkat kerasnya. Pada gambar di bawah, delapan node elips adalah input potensial ke CLB yang disebut DD. Hanya satu node (maksimum) yang dapat dikonfigurasi sebagai input, karena menghubungkan dua sinyal ke satu input dapat mempersingkat keduanya.

Pemilihan input. Delapan input yang dilingkari hijau adalah input DD potensial, hanya satu yang dapat dipilih.

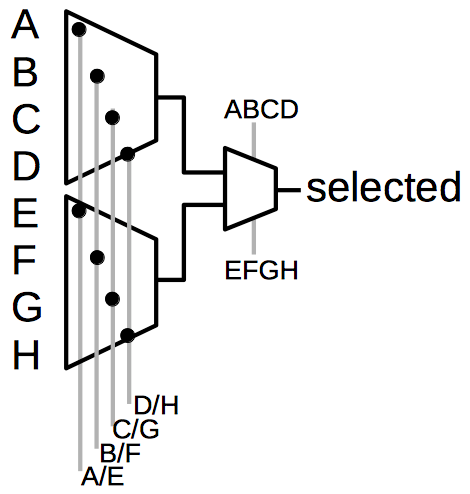

Input yang diperlukan dipilih oleh multiplexer. Solusi langsungnya adalah dengan menggunakan multiplexer 8-input dengan tiga bit kontrol memilih salah satu dari 8 sinyal. Solusi langsung lainnya adalah dengan menggunakan transistor 8 pass, masing-masing dengan sinyal kontrolnya sendiri, salah satunya memilih sinyal yang diperlukan. Namun, FPGA menggunakan pendekatan hybrid yang menghilangkan kebutuhan decoder dalam kasus pertama, tetapi membutuhkan 5 sinyal kontrol, bukan 8 yang diperlukan dalam pendekatan kedua.

FPGA menggunakan multiplexer untuk memilih salah satu dari delapan input.

Diagram pada gambar di atas menunjukkan multiplexer dua lapis yang digunakan dalam FPGA. Pada tahap pertama, salah satu sinyal kontrol diaktifkan. Pada tahap kedua, sinyal tinggi atau rendah dipilih dan diterapkan ke keluaran. Misalnya, sinyal kontrol B / F diterapkan ke tahap pertama, dan ABCD ke tahap kedua, masukan B akan menjadi satu-satunya yang menuju ke keluaran. Artinya, memilih salah satu dari delapan input membutuhkan 5 bit di bitstream dan menggunakan 5 lokasi memori.

Masukkan CLB multiplekser

CLB. EFGH ABCD, . -, CLB 6 10 , , . , , , , . , , 6 , . , , .

Kesimpulan

XC2064 menggunakan berbagai jaring yang sangat dioptimalkan untuk mengimplementasikan blok logika dan interkoneksi jaringan. Rantai ini harus dikemas dengan rapat agar pas dengan kristal. Meski begitu, XC2064 adalah chip yang sangat besar, lebih besar dari mikroprosesor pada saat itu, dan sulit untuk diproduksi, dengan biaya ratusan dolar. Dibandingkan dengan FPGA modern, XC2064 memiliki jumlah sel yang sangat kecil, tetapi bahkan itu adalah awal dari lini produk baru yang revolusioner.

Dua konsep adalah kunci untuk memahami bitstream XC2064. Pertama, FPGA diimplementasikan atas dasar 64 ubin, blok berulang yang menggabungkan blok logis dan interkoneksi. Meskipun FPGA digambarkan memiliki blok logika yang dikelilingi oleh interkoneksi, namun tidak diterapkan seperti itu. Konsep kedua adalah bahwa aliran bit tidak didasarkan pada abstraksi apa pun, bitstream secara langsung memetakan pengemasan dua dimensi sel memori FPGA. Jadi, bitstream hanya masuk akal jika Anda mempertimbangkan struktur fisik FPGA.

Catatan

, XC2064 (. 11), CLB . , , 20% , . — -, . , . .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

, 8×18. , , . .

. , #1 () #2 () . 8 #1 1 8 . #2 , . , "#2: 1-3" , 1 3 #2. «ND», , . ND ND.

, . , PIP , , . () (1, 2, 3), Y (). (-) -. , , . (), D (), A () . CLB, . , . X Y (LUT) F G. LUT. LUT F LUT G, . , 8 LUT , .

Saya telah mengumumkan posting terakhir saya di twitter, jadi ikuti kenshirriff . Saya juga memiliki RSS feed . Terima kasih kepada John McMaster, Tim Ansell dan Philip Freidin untuk diskusi-diskusi tersebut.