terakhir: transceiver UART siap pakai yang dirakit dari IC seri 7400

Pertama-tama, mari kita cari tahu apa itu UART... Ini adalah transceiver asinkron universal - protokol sederhana yang memungkinkan Anda mengirim dan menerima data 8-bit secara asinkron sehingga prosesor atau komputer dapat berkomunikasi dengan dunia luar. Ini berguna dengan sendirinya - komputer 8-bit saya dapat berkomunikasi dengan laptop dan menggunakan program pemantauan port serial (seperti putty ) sebagai antarmuka untuk input dan output teks. Yang lebih menarik, saya dapat memprogram bootloader OS untuk komputer 8-bit saya, dan kemudian memprogramnya melalui koneksi UART dari laptop! Karena modul Bluetooth tipe HC-05 pada dasarnya berkomunikasi dengan CPU melalui UART, saya bahkan dapat menggunakan modul Bluetooth untuk memprogram komputer 8-bit saya dari kejauhan! Ini akan mengagumkan.

Beberapa puritan akan menganggap pemrograman komputer 8-bit dengan komputer yang jauh lebih kuat sebagai pendekatan yang curang - tapi ini adalah proyek saya dan itu sesuai dengan aturan saya! Harap program mesin buatan tangan dengan sakelar DIP jika Anda menyukai entri data daripada pemrograman dan menginginkan pengalaman kerja keras yang autentik.

Apa pun itu dengan pemrograman, setidaknya saya memutuskan untuk membatasi diri saat mengembangkan komputer ke chip TTL sederhana - tidak ada Arduino, Raspberry Pi, ESP8266 dan modul Turing-complete lainnya (kalau tidak, apa yang menarik?).

Protokol UART dan batasan desain

Sebelum Anda adalah struktur sinyal UART. Ini memiliki bit awal, dilambangkan dengan transisi sinyal yang tinggi ke rendah, diikuti oleh byte data (LSB pertama), dan kemudian bit stop, yang mendorong sinyal tinggi. Terkadang ada juga bit paritas, tetapi tidak diperlukan, jadi saya menghilangkannya karena alasan kesederhanaan. Waktu transmisi untuk setiap bit ditentukan oleh baud rate (dalam hal ini, bit per detik). Misalnya, baud rate 9600 berarti bit ditransmisikan dalam

1/9600 = 104 μs. Bentuk gelombangnya cukup sederhana, jadi kami dapat menerapkannya sepenuhnya di perangkat keras pada chip logika.

Saya harus memilih osilator kristal yang akan memberi saya akses ke baud rate standar, lebih disukai dapat dibagi dengan dua pangkat, sehingga akan lebih nyaman untuk beroperasi dengan penghitung biner. Setelah beberapa pemikiran, saya memutuskan untuk menggunakan osilator 2,4576 MHz, karena memungkinkan transfer pada 38400 bps (dibagi 64), atau 9600 bps (dibagi 256).

Pemancar UART

Daftar komponen:

- Osilator kristal 2,4576 MHz

- Penghitung 4-bit 3 x 74LS161

- 74LS674 register geser 16-bit

- 74LS06 DAN

- 74LS74 D-trigger

- 74LS04 TIDAK

- Dioda 1N4001

- 470 uF (!) Kapasitor (penghalusan daya)

Skema

Sirkuit pemancar UART adalah yang paling mudah dipahami. Pada dasarnya, ini adalah register geser beban paralel dengan output serial. Ini memuat byte data, melacak bit awal dan akhir, dan menyinkronkannya dengan baud rate yang diinginkan. Diagram di bawah menunjukkan proses ini. Pada bagian (1), osilator kristal 2,4576 MHz diperlambat menjadi 38 400 Hz menggunakan dua pencacah 74LS161 4-bit. Pada bagian (2), register geser 16-bit 74LS674 digunakan untuk menyinkronkan data untuk UART. Saya menggunakan register ini karena saya sudah memilikinya. Saya mengerti bahwa IC ini mahal dan mungkin sulit ditemukan, tetapi ini pasti menyederhanakan seluruh skema saya.

Dengan hanya tiga IC ini (dua pencacah 4-bit dan register geser), Anda dapat mengirim aliran karakter secara terus menerus ke pemancar UART pada 38.400 bps (tanpa paritas)! Ya, ini adalah aliran berkelanjutan - Saya tidak memperhitungkan bahwa register geser memperbarui buffer beban dalam lingkaran - oops. Saya tidak memerlukan perilaku ini - Saya ingin prosesor mengirim satu byte pada satu waktu. Semuanya diperumit oleh fakta bahwa pulsa clock prosesor dan UART tidak disinkronkan, dan saya tidak ingin membuat asumsi tentang timer siapa yang lebih cepat, sinyal mana yang relevan pada saat apa, dll. Karena saya perlu menangani asinkron dengan andal, saya memutuskan untuk menggunakan skema berikut yang berfungsi dengan baik:

- (3) Prosesor mengirimkan sinyal "transfer byte" yang tidak sinkron dengan prosesor dan jam UART.

- «». ( AND 74LS06 D- 74LS74).

- UART «» 4- 74LS161. UART.

- (4) 16 , .

Perhatikan bahwa saya menggeser 16 bit daripada 10 bit sinyal pemancar UART - terutama karena kenyamanan menggunakan bit pembawa untuk menonaktifkan sirkuit transmisi. Saya dapat menggunakan penghitung desimal (misalnya, 74LS162), tetapi saya tidak memilikinya ketika saya memasang sirkuit di papan tempat memotong roti. Mungkin dalam skema terakhir saya akan beralih ke sana.

Penerima UART

Daftar komponen:

- Osilator kristal 2,4576 MHz (Anda dapat menggunakan osilator yang sama dengan penerima)

- Penghitung 4-bit 3 x 74LS161 (dapat menggunakan salah satu IC dari penerima)

- 74LS74 D-trigger

- 74LS04 TIDAK (dapat menggunakan IC penerima)

- Dioda 1N4001

- 470 uF (!) Kapasitor (penghalusan daya)

- Resistor 220 ohm dan LED untuk kecantikan.

Menurut saya, jika pemancar UART yang dijelaskan di atas mudah dipahami, penerima akan menjadi agak lebih rumit. Namun, apa yang baik dengan logika digital adalah ia dapat dipecah menjadi modul terpisah, dan kemudian semuanya tidak lagi tampak rumit!

Bentuk gelombang di sudut kiri bawah diagram di bawah ini menunjukkan apa yang harus dipertimbangkan saat menerima bit pemancar digital tunggal. Bagaimana kita tahu jika satu byte sedang dikirimkan kepada kita? Mudah - bit awal ditandai dengan transisi tinggi ke rendah, jadi kita dapat membalikkannya dan menggunakan transisi rendah ke tinggi untuk menyetel D-flip-flop (74LS74) (2).

Sekarang kita perlu mulai menulis sinyal dengan menggesernya ke register geser dan mengambil sampel di tengah urutan bit data. Yang penting untuk dipahami: karena kita tidak tahu kapan kita akan mulai menerima data dari UART, proses ini tidak akan sinkron dengan pulsa jam kita. Oleh karena itu, semakin cepat impuls kita, semakin dekat kita dengan asal sebenarnya dari sinyal pemancar. Demi kenyamanan, kecepatan clock saya 16 kali baud rate (1). Ini berarti bahwa setiap bit yang ditransmisikan melewati 16 pulsa generator ini. Oleh karena itu, untuk mengambil sampel kira-kira di tengah data yang ditransmisikan, kita harus melakukannya pada hitungan 8 - untuk ini kita menghasilkan sinyal SAMPLING_CLK (3).

Kemudian, di tepi naik jam baru ini, kita dapat menyinkronkan sinyal yang ditransmisikan dengan dua register Pergeseran Output Paralel Seri (SIPO) 8-bit yang terkait di tengah setiap bit data. Pada hitungan ke-16, kami berakhir dengan bit digital, jadi kami menambah penghitung lain yang melacak jumlah total bit yang disinkronkan di (5). Ketika penghitung ini mencapai 16 (bisa jadi penghitung desimal), sirkuit penerima dinonaktifkan dengan membersihkan flip-flop D. Fiuh! Saya memberikan diagram di bawah ini, dan saya harap Anda dapat melacak logika operasinya menggunakan deskripsi saya.

Sayangnya, saya tidak memiliki osiloskop, dan awalnya rangkaian saya memberikan beberapa hasil misterius, menerima satu byte, dan kemudian menerima byte lain dengan cara yang berbeda. Saya mengubah osilator 2,4576 MHz untuk osilator 555 1 detik untuk memeriksa logika penghitungan, dan saya menemukan masalah dengan input mengambang pada pin salah satu penghitung (saya men-debug menggunakan LED). Saya mengikat kedua pin reset counter ke sinyal RX_active, menyebabkan counter untuk beralih antara on dan reset, yang menghapus outputnya di akhir setiap siklus akuisisi data. Penghitung sekarang bekerja seperti yang diharapkan, dan ketika saya menyalakan kembali generator pada 2.4576 MHz semuanya mulai bekerja dengan benar dan andal.

Rangkaian komputer terakhir pada papan tempat memotong roti akan memiliki register keluaran untuk mengontrol keluaran data ke bus. Akhirnya, saya menggunakan D-flip-flop tambahan pada 74LS74 untuk mengimplementasikan sinyal RX_READY, yang dapat dibaca oleh prosesor untuk memeriksa apakah byte sudah siap untuk dibaca (itu benar hanya ketika byte diterima sepenuhnya).

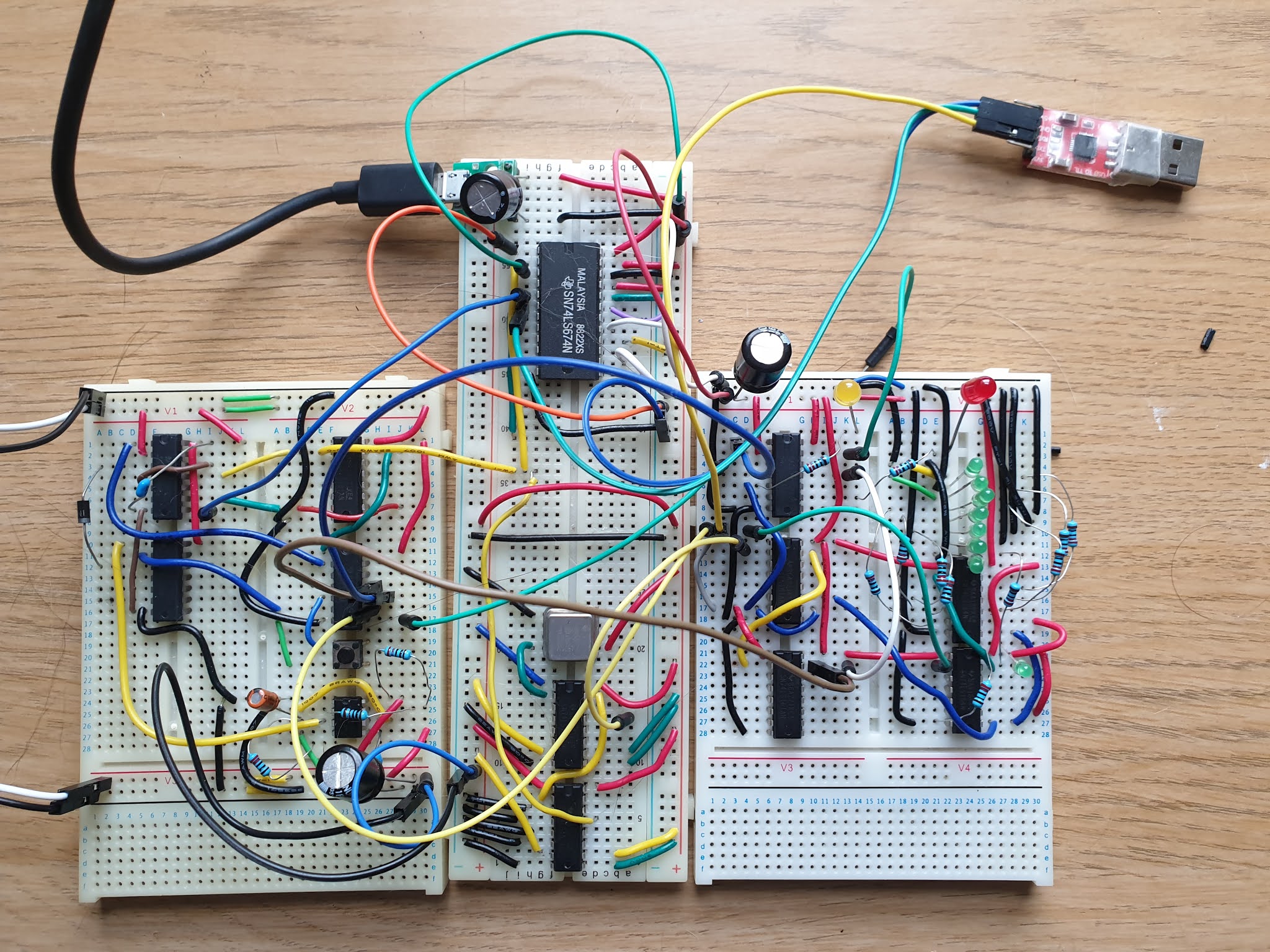

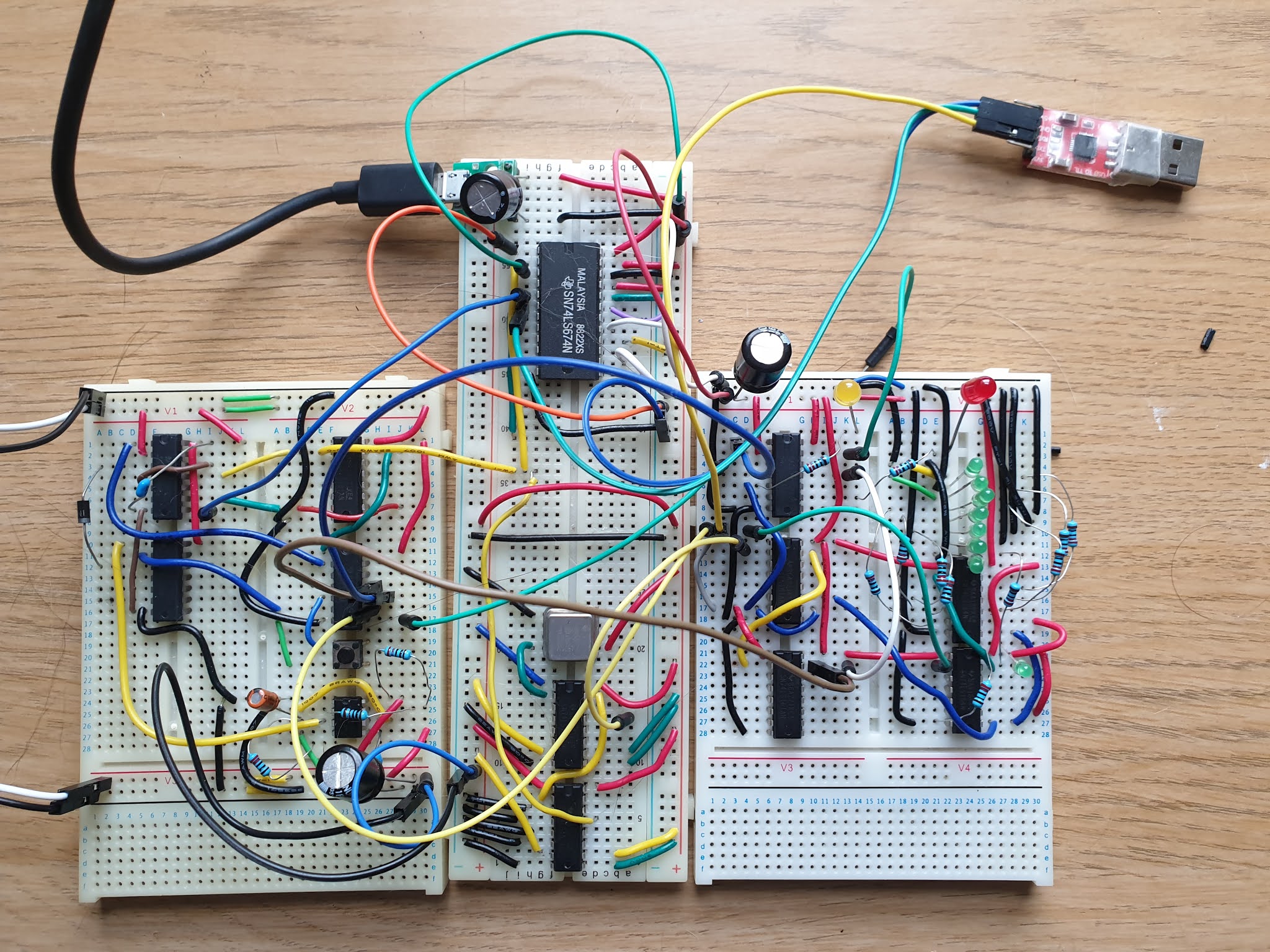

Di bawah ini adalah foto komputer yang dirakit dan berfungsi. Antarmuka UART-USB adalah dongle di kanan atas. Papan tengah berisi osilator kristal dan penghitung 4-bit yang menghasilkan berbagai pulsa clock. Di bagian atas, di samping daya USB, adalah register geser 16-bit. Papan kiri berisi logika untuk pengiriman terkontrol dari satu byte (UART TX). Anda dapat melihat tombol yang saya gunakan untuk mensimulasikan sinyal kontrol prosesor dan timer 555, yang bertindak sebagai pulsa clock prosesor. Modul UART RX berada di papan kanan. LED hijau menunjukkan penerimaan byte pada input, LED kuning menunjukkan penerimaan data (sinyal sibuk UART RX), dan LED merah menyala ketika byte siap dibaca oleh prosesor.

Mencari papan tempat memotong roti yang lebih cantik dan keterampilan kabel

Tambahan

Saya mengoptimalkan rangkaian sedikit (di sepanjang jalan, setelah belajar tentang perbedaan antara memproses peristiwa asinkron dan sinkron dalam logika IC diskrit). Saya ingin mengurangi jumlah chip dengan menggunakan penghitung desimal yang akan menghitung bit yang masuk, dan menghitung 10 bit, bukan 16. Kemudian saya bisa menghapus register geser.

Saya pertama kali mencoba penghitung 74LS162. Untuk satu byte, semuanya berfungsi, tetapi saya segera menemukan bahwa ia memiliki mekanisme reset sinkron - yaitu, dibutuhkan satu siklus clock untuk mengatur ulang sinyal. Karena jam berhenti setelah bit terakhir diterima, penghitung tidak dihapus. Penghitung 4-bit 74LS161 yang saya hapus memiliki reset asinkron, jadi semuanya berfungsi sebelumnya. Ada baiknya kami menemukan penghitung desimal dengan reset asinkron - 74LS160. Semuanya bekerja dengan baik dengannya - lihat diagram yang diperbarui.

Memeriksa kesalahan dalam byte yang diterima

Untuk kesederhanaan, saya belum menambahkan pengecekan kesalahan pada byte yang dihasilkan. Anda dapat membayangkan bahwa kami menambahkan bit paritas dan beralih flip-flop setiap kali "1" diterima. Kemudian kita akan tahu apakah kita menerima jumlah bit genap atau ganjil, dan dapat membandingkannya dengan bit paritas dengan menyetel bendera jika tidak cocok. Selain itu, dimungkinkan untuk menyertakan cek konfirmasi bahwa bit stop sama dengan "1". Untuk menghemat ruang, saya tidak menambahkan fungsi ini, tetapi saya ingin menambahkannya di masa mendatang. Modularitas proyek memungkinkan Anda melakukan ini sesuai kebutuhan.

Catatan

Saya suka komputer 8-bit di papan tempat memotong roti dan senang melakukan proyek mini ini. Saya telah mendesain sirkuit ini cukup lama, dan saya masih terkejut ketika saya menggabungkannya dan semuanya bekerja. Ini semacam keajaiban! Hampir.