Artikel sebelumnya dalam seri ini

Bagaimana cara kerja program komputer biasa? Ada lingkungan eksternal tertentu (monitor dan keyboard dengan "mouse" adalah perwakilan paling khas dari lingkungan ini). Program berinteraksi dengan mereka. Saat men-debug, Anda dapat membuat pengaruh nyata dari lingkungan eksternal, atau Anda dapat meniru mereka. Penguji kami sering menulis semua jenis skrip yang hanya meniru pengaruh eksternal. Setelah itu, penganalisis log diluncurkan, yang memeriksa bahwa jawaban sudah benar pada hari Rabu.

Bagaimana jika semuanya buggy di program komputer ini? Anda dapat mengatur breakpoint dan memeriksa snapshot dari sistem pada saat mereka mencapai. Sepotong sistem adalah nilai variabel. Mungkin status berbagai mutex dan objek sinkronisasi lainnya. Secara umum, snapshot dari parameter internal dari sistem yang di-debug.

Saat men-debug untuk FPGA, Anda dapat melakukan hal yang sama. Benar, jika lingkungan itu nyata, maka berhenti dan mempelajari suatu bagian dari sistem itu bermasalah, meskipun mungkin. Sebagai bagian dari cerita tentang Redd, saya terus mempromosikan gagasan bahwa semuanya harus sederhana dan cepat. Kami tidak merancang sistem yang rumit. Kami melakukan beberapa jenis modul, seperti yang telah dilakukan di artikel sebelumnya . Ini canggih, tetapi sangat, sangat tidak rumit. Secara umum kita akan melakukan pemodelan perilakunya.

Dan di sini muncul pertanyaan tentang lingkungan luar. Bagaimana cara mensimulasikannya? Model datang membantu kami. Verilog (serta VHDL dan yang serupa lainnya) sangat mungkin untuk menggambarkan perilaku apa pun. Kami membuat sistem yang bekerja dengan sirkuit mikro ULPI ... Jadi, untuk menguji operasinya, pasti ada sesuatu di ujung lain yang berperilaku persis seperti ULPI. Yaitu, model ULPI. Tapi ini belum cukup. Blok kami bereaksi terhadap perintah dari bus ALAVON_MM. Bus inilah yang membuat blok itu hidup. Oleh karena itu, kami juga perlu menambahkan model bus AVALON_MM, dan model ini harus aktif. Dialah yang akan mengirimkan pengaruh tes.

Pada akhirnya kita harus membuat sistem seperti itu. Dan kemudian kita akan dapat merekam diagram pengaturan waktu sinyal pada semua busnya dan bahkan di dalam modulnya. Jika terjadi kesalahan, kita dapat mengatur breakpoint dan memeriksa snapshot dari sistem untuk menemukan musuh. Meskipun, secara pribadi, saya biasanya tidak menetapkan breakpoint ini, paling sering analisis diagram waktu sudah cukup. Faktanya adalah bahwa sinyal dapat dilihat tidak hanya sinyal antarmuka, tetapi juga sinyal internal. Menarik selusin atau dua sinyal internal pada grafik, Anda biasanya dapat menebak apa yang salah diterapkan dalam logika.

Tujuan artikel hari ini bukan untuk membicarakan tentang apa itu pemodelan secara umum (ini adalah cerita yang panjang), tetapi untuk menunjukkan bagaimana melakukan pemodelan ini paling cepat. Dan kami akan mempertimbangkan ini bukan pada misi tempur, tetapi pada contoh sederhana. Kami akan membuat sistem pengujian yang sangat sederhana sehingga di artikel berikutnya kami sudah memahami dari mana kaki versi yang lebih kompleks itu tumbuh, karena ketika membaca lebih nyaman untuk tidak duduk dan bertanya-tanya: "Mengapa dia melakukan ini?", Tetapi untuk mengetahui semua prinsip dasar, dari mana komplikasi sudah mengikuti ... Ngomong-ngomong, baru-baru ini ternyata salah satu kenalan saya, meskipun dia memiliki keterampilan pemodelan, tidak tahu bahwa lingkungan Quartus memiliki mekanisme bawaan yang memungkinkan Anda melakukan ini dengan mudah dan alami. Dia menghabiskan lebih banyak usaha untuk itu daripada yang dibutuhkan. Jadi mungkin seseorang, juga, sekarang akan mempelajari sesuatu yang baru untuk diri mereka sendiri tentang kemungkinan yang melekat di Quartus. Begitu,ayo kita mulai.

Verilog

Orang-orang terbagi dalam dua kategori. Mereka yang suka membuat segalanya dari awal dengan tangan mereka dan mereka yang suka melakukannya dengan mengutak-atik mouse. Untuk membuat segalanya dengan tangan Anda lebih benar. Anda dapat mengontrol setiap tindakan dan melakukan semua yang Anda ketahui dengan sempurna. Tapi ingatan tidak bisa diandalkan. Jika dia melakukan hal yang sama sepanjang waktu, dia akan mengingat detailnya, dan jika dia harus beralih antar bahasa sepanjang waktu, setelah satu atau dua bulan dia harus mengingat apa yang perlu dilakukan di sana. Oleh karena itu, bekerja melalui opsi "bermain-main dengan mouse" memiliki hak untuk ada setidaknya karena ini. Sekali lagi, jika modul yang di-debug memiliki selusin atau lebih sinyal antarmuka, saya selalu bosan melakukan pekerjaan rutin untuk mendeklarasikan ulang dan meneruskannya. Oleh karena itu, sekarang kita akan melihat bagaimana membuat model dengan menggunakan mouse. Dan kemudian - setiap orang akan memutuskan sendiri apakah ini cukup untuknya, atau haruskah dia beralih ke pekerjaan manual.

Jadi, kami ingin mensimulasikan modul. Apa yang "mensimulasikan" berada di luar cakupan siklus kami, Anda dapat menulis siklus besar yang terpisah tentang topik ini. Artinya, dalam kerangka bagian ini, kami berasumsi bahwa Anda sudah familiar dengan metodologi untuk mengembangkan model. Tapi kemudian semuanya perlu dimasukkan dalam proyek ... Atau tidak? Anehnya, Anda bahkan tidak perlu membuat proyek Anda sendiri untuk membuat model modul. Kami dapat menempelkan dirinya sebagai parasit ke proyek apa pun, tanpa menyertakan sesuatu yang baru di dalamnya, tetapi hanya dengan membuat rangkaian pengujian yang tidak akan berpartisipasi dalam perakitan utama dengan cara apa pun.

Demi kepentingan, mari lampirkan ke proyek ULPI kami modul lucu di SystemVerilog, yang ditulis oleh saya khusus untuk ilustrasi dan tidak ada hubungannya dengan penganalisis yang dikembangkan. Beberapa waktu yang lalu saya banyak bermain-main dengan menghitung checksum, jadi itu muncul di kepala saya.

module sum(

input clk,

input [7:0] data,

input we,

input sof,

output [15:0] sum

);

logic [15:0] temp;

always @ (posedge clk)

begin

if (we)

begin

if (sof)

temp <= data;

else

temp <= temp + data;

end

end

// -

//assign sum = (~temp)+1;

// :

assign sum = temp;

endmodule

Dapat dilihat bahwa data datang melalui bus, yang sangat mirip dengan AVALON_MM, dan hanya dikeluarkan dalam kode paralel.

Mari kita letakkan file yang dihasilkan di direktori dengan proyek kita, tetapi kita tidak akan memasukkannya ke dalam proyek di Quartus. Sebagai gantinya, kami akan membuat rangkaian pengujian khusus untuk itu. Untuk melakukan ini, pilih item menu Assignments—> Settings:

dan di pohon yang muncul, cari item EDA Tools Settings—> Simulation:

Ngomong-ngomong, tentang jenis simulasi yang disorot oleh bingkai hijau. Mungkin seseorang ingat bahwa di artikel pertama saya mengatakan bahwa ketika membuat proyek, semata-mata karena kebiasaan, saya memilih ModelSim Altera? Itu adalah senjata di atas panggung yang cepat atau lambat harus ditembakkan. Namun, jika jenis pemodelan tidak dipilih saat proyek dibuat, Anda dapat memilih atau mengubahnya di sini.

Kami terus membuat rangkaian pengujian. Alihkan tombol radio ke Compile test bench (ngomong-ngomong, bagaimana istilah ini diterjemahkan dengan indah ke dalam bahasa Rusia? Saya tidak dapat memaksa diri saya untuk menulis "bangku tes", karena saya tidak melihat bangku apapun) dan tekan tombol Test Benches :

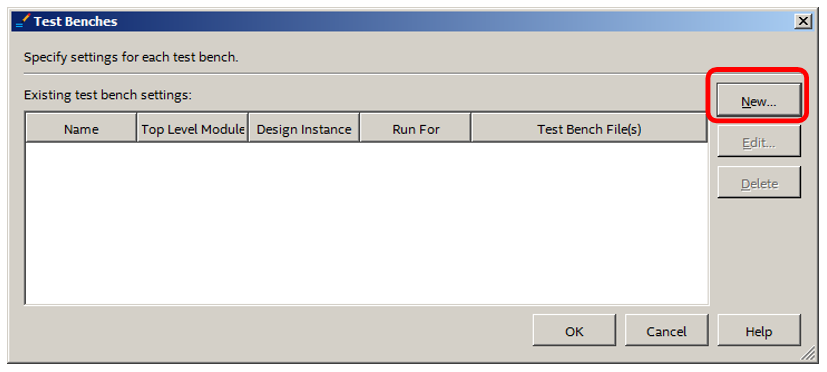

Pada dialog yang terbuka, tekan New :

If to do uji kasus secara manual, Anda dapat mengisi kolom dalam satu kali lulus. Tetapi karena kita melakukan semuanya dengan mouse, sekarang kita hanya mengisi sebagian bidang, dan sisanya akan kita isi nanti. Di kolom Test bench nameSaya mengetik kata Parazit (apa lagi yang disebut tes yang hanya menjadi parasit pada proyek?). Kata Parazit di bawahnya diisi secara otomatis. Sekarang kami tidak akan mengubahnya, tapi di masa depan kami tetap harus melakukannya. Juga, dengan menggunakan tombol "...", saya memilih file sum.sv dengan kode penambah untuk di-debug, dan kemudian, menggunakan tombol Tambah , mendorongnya ke dalam daftar file uji. Untuk saat ini, itu saja. Menutup dialog ...

Selanjutnya, kami akan melanjutkan untuk membentuk pengujian di lingkungan ModelSim. Untuk melakukan ini, pilih Tools—> Run Simulation Tools—> item menu Simulasi RTL:

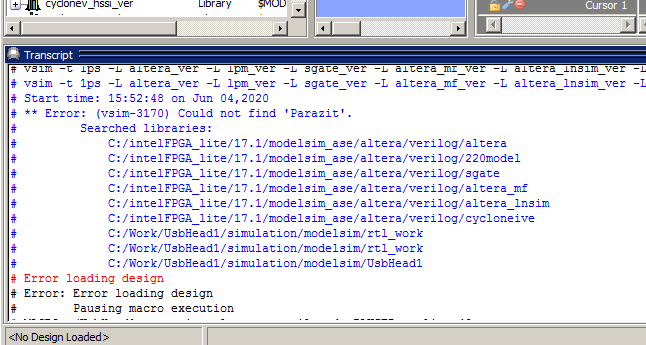

Jendela ModelSim terbuka. Mungkin kesalahan akan ditemukan dalam kode Verilog, maka Anda perlu menutup ModelSim, memperbaiki kesalahan, dan membukanya kembali. Tetapi cepat atau lambat, daftar kesalahan akan menjadi murni organisasi. Ini terlihat seperti ini bagi saya:

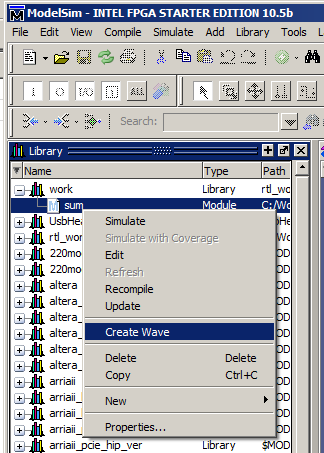

Tidak ditemukan modul tingkat atas. Ini normal. Kami belum membuatnya dengan sederhana. Oleh karena itu, kami bekerja di daftar perpustakaan dan membukanya. Ini dia, penambah kami.

Arahkan kursor ke atasnya, tekan tombol kanan mouse dan pilih item menu Buat Gelombang. Ini semua sangat membosankan dalam teks, jika saya merekam video, seluruh proses akan memakan waktu puluhan detik, jadi jangan khawatir, tetapi perhatikan tangan Anda lebih jauh. Jadi, Buat Gelombang ...

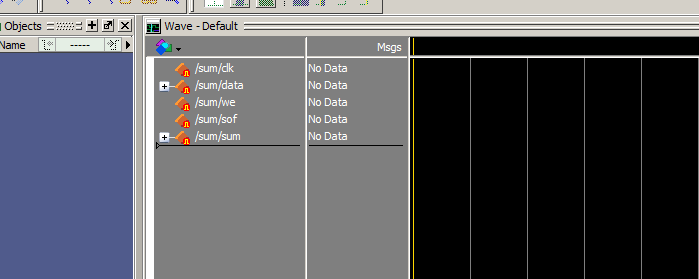

Sinyal antarmuka modul secara otomatis pindah ke grafik:

Anda perlu menetapkan nilai ke salah satunya. Tidak masalah yang mana, penting untuk diangkat. Lingkungan pemodelan Quartus yang sangat tua bagus dalam menghasilkan sinyal jam. Sayangnya, itu sudah lama ditarik dari pengiriman, sejak mereka mulai memasang ModelSim, dan di sini semuanya tidak begitu indah dengan sesuatu seperti itu. Saya tidak melihat gunanya membuat generator di sini, jadi saya bahkan tidak akan menampilkannya. Jadi ... Baiklah, mari kita atur garis kita ke nol. Kita arahkan ke sinyal, tekan tombol kanan, pilih item menu Edit—> Editor Gelombang—> Buat / Modifikasi WaveForm.

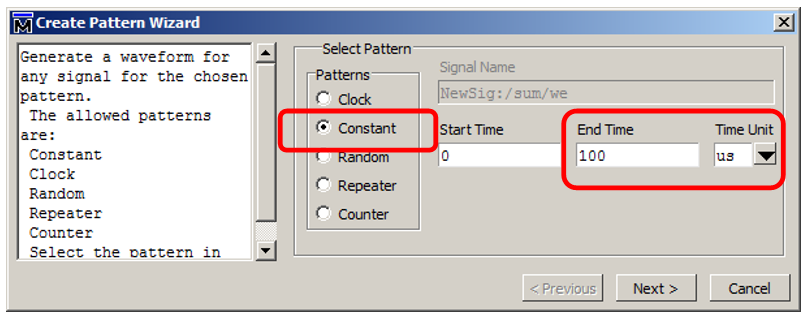

Pada dialog yang muncul, pilih Constant . Dan pada saat yang sama kami akan mengubah waktu, katakanlah, dengan 100 mikrodetik:

Selanjutnya, kami menunjukkan nilai 0:

Kami telah membuat kumpulan data minimum yang diperlukan, dan sisanya akan lebih mudah dilakukan dengan pena. Kami mengekspor file. Untuk melakukan ini, pilih item menu File—> Ekspor—> Bentuk Gelombang:

Pilih jenis file Verilog Testbench (sayangnya, ini bukan SystemVerilog, tetapi di masa mendatang dimungkinkan untuk memperbaikinya dengan pena). Kami juga mengatur nama file. Saya menamakannya parazit_tb , mengikuti "mengapa tidak?"

Itu saja, ModelSim bisa ditutup, sedangkan rumah sementara tidak perlu diselamatkan.

Apa yang harus dilakukan dengan model selanjutnya

Ini adalah file Verilog yang bengkok, tetapi masih siap pakai, sistem dibuat untuk kita:

`timescale 1ns / 1ns

module parazit_tb ;

reg sof ;

reg we ;

wire [15:0] sum ;

reg [7:0] data ;

reg clk ;

sum

DUT (

.sof (sof ) ,

.we (we ) ,

.sum (sum ) ,

.data (data ) ,

.clk (clk ) );

// "Constant Pattern"

// Start Time = 0 ns, End Time = 100 us, Period = 0 ns

initial

begin

end

initial

#0 $stop;

endmodule

Otomatisasi menyelamatkan kita dari menulis blok bangunan. Selain itu, jika ada lebih banyak sinyal antarmuka, otomatisasi akan mendaftar dan menghubungkan semua sirkuit dengan patuh. Secara pribadi, saat membuat rangkaian pengujian secara manual, itu adalah proses mendeskripsikan sinyal dan penerusannya yang membuat saya depresi. Sekarang, di file ini, kita sekarang akan membuat model lingkungan yang akan mempengaruhi modul jumlah yang di- debug .

Seperti yang Anda lihat, tidak ada gunanya mengatur konstanta yang dibuat oleh osilator. Tapi semua sama, semua sirkuit sudah dibuat, modul yang akan diuji terhubung, bahkan bagian awal sudah dibuat. Mari perbaiki kodenya. Pertama, kami akan menghapus breakpoint dengan menghapus garis:

initial

#0 $stop;

Selanjutnya, kami akan menambahkan model generator jam (betapa saya merindukan generator indah yang dibuat oleh Quartus lama! Di sana Anda dapat mengatur frekuensi dalam megahertz dan tidak berpikir untuk menghitung ulang menjadi periode, dan terlebih lagi - setengah periode).

always

begin

clk = 0;

#5;

clk = 1;

#5;

end

Sekarang kita perlu mengirim beberapa byte data. Cara termudah untuk melakukannya adalah tepat di bagian awal , tetapi jika saya menulis setiap fase akses bus di sana, kode di bagian ini akan membingungkan. Oleh karena itu, saya akan melakukan tugas berikut (dialah yang bertindak sebagai model ban):

task SendByte (input reg[7:0] D);

begin

data = D;

we = 1;

@(posedge clk);

#1

we = 0;

end

endtask

Nah, saya akan menulis tujuan dari konstanta dan panggilan siklus untuk bekerja dengan bus di blok awal . Izinkan saya mengingatkan Anda bahwa jenis catatan # 123 berarti "tunggu 123 unit waktu". Kami memilikinya dalam nanodetik. Saya juga mengingatkan Anda bahwa karena penugasannya berurutan, kami menggunakan operasi "sama", bukan "panah". Jadi, kami memiliki kode pengujian utama berikut:

Tonton di sini

initial

begin

sof = 0;

we = 0;

data = 0;

#13;

//

sof = 1;

SendByte (1);

//

sof = 0;

SendByte (5);

SendByte (1);

//

#20;

SendByte (1);

end

Secara total, kode modul lengkap kami terlihat seperti ini:

Lihat kode modul lengkap.

`timescale 1ns / 1ns

module parazit_tb ;

reg sof ;

reg we ;

wire [15:0] sum ;

reg [7:0] data ;

reg clk ;

sum

DUT (

.sof (sof ) ,

.we (we ) ,

.sum (sum ) ,

.data (data ) ,

.clk (clk ) );

always

begin

clk = 0;

#5;

clk = 1;

#5;

end

task SendByte (input reg[7:0] D);

begin

data = D;

we = 1;

@(posedge clk);

#1

we = 0;

end

endtask

// "Constant Pattern"

// Start Time = 0 ns, End Time = 100 us, Period = 0 ns

initial

begin

sof = 0;

we = 0;

data = 0;

#13;

//

sof = 1;

SendByte (1);

//

sof = 0;

SendByte (5);

SendByte (1);

//

#20;

SendByte (1);

end

endmodule

Menyelesaikan persiapan kasus uji

Saatnya menambahkan teks ini ke rangkaian pengujian. Untuk melakukan ini, pergi ke dialog yang sudah kita kenal. Tapi

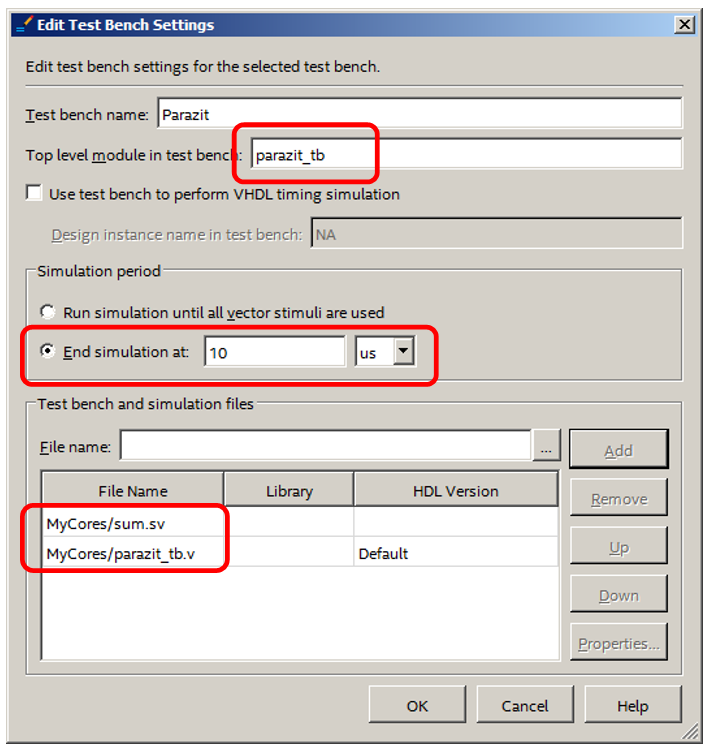

sekarang kita tidak membuat set kita, tapi pilih dari daftar. Di masa mendatang, daftar akan bertambah seiring set ditambahkan ... Setelah dipilih, tekan tombol Edit. Saya membuat tiga pengeditan pada pengaturan:

- Menambahkan file parazit_tb.v ke daftar.

- Karena dalam file parazit_tb.v modul tingkat atas memiliki nama parazit_tb (Anda dapat memastikan dengan melihat sumber dari bagian sebelumnya), saya memasukkan nama ini di modul Tingkat atas di baris bangku tes .

- Saya berkata untuk menjalankan simulasi selama 10 mikrodetik dan kemudian berhenti. Jika ada, saya akan melakukannya dengan menekan tombol kontrol manual.

Total

Kami menutup semuanya. Jalankan ModelSim lagi. Kami melihat bahwa semuanya bekerja dengan benar. Data masuk dan dihitung jumlahnya. Jika tidak ada data pada jam ( kami nol), jumlahnya tidak bertambah.

Cara menggunakan lingkungan pemodelan itu sendiri adalah topik untuk beberapa artikel. Dan lebih cenderung dalam format video. Namun secara umum, kami mengenal metode persiapan dan menjalankan pengujian dengan cepat dalam bahasa Verilog dari lingkungan Quartus.

Sekarang kita tahu cara menjalankan simulasi dengan cepat, kita dapat membuat sketsa model lingkungan untuk kepala penganalisis USB dan mengujinya. Pada saat yang sama, kami tidak menghafal satu mantra ModelSim, karena Quartus memungkinkan Anda untuk mengkonfigurasi semuanya dengan menggunakan "mouse". Dia menghasilkan semua skrip yang diperlukan sendiri dan menyebut lingkungan ModelSim itu sendiri. Kami juga membuat basis untuk model dalam mode otomatis, meskipun kami kemudian harus memodifikasinya secara manual.

Aduh dan ah. Salah satu elemen lingkungan eksternal adalah modul ULPI. Untuk mengembangkan modelnya sendiri, pertama-tama Anda harus memahami logika pengoperasian sirkuit mikro itu dengan cermat. Dan di artikel sebelumnya saya mengatakan bahwa itu sangat rumit. Dan, kedua, Anda perlu menghabiskan banyak waktu untuk mengembangkan kode model. Dan penghapusan kesalahan di dalamnya ... Jelas bahwa lebih mudah untuk menemukan sesuatu yang siap. Tetapi model yang sudah jadi hanya ditemukan dalam bahasa SystemC. Oleh karena itu, pada artikel selanjutnya, kita akan belajar membuat model sistem menggunakan bahasa ini.