pengantar

Batasan waktu adalah beberapa informasi, yang menggunakan utilitas analisis waktu dalam sistem CAD dapat menghitung apakah data akan berhasil melewati semua register proyek. Pengguna harus menghitung sendiri batas ini dan menuliskannya di file batas waktu. Tanpa batasan ini, pengguna menulis proyek secara acak, tanpa memeriksa kinerjanya, dan kompilator akan bersumpah bahwa ia tidak menemukan batasan apa pun.

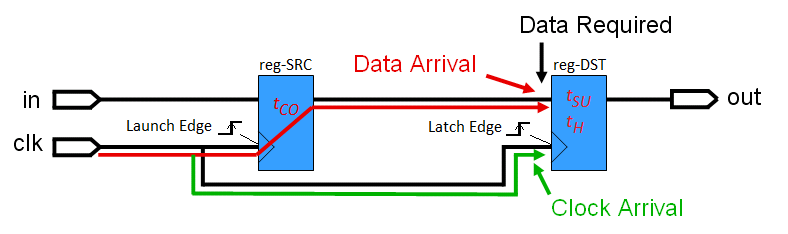

Di artikel sebelumnya ( tautan) Saya berbicara tentang transfer data antara dua register dan bagaimana eksekusi hubungan waktu dihitung dalam kasus transfer data di dalam FPGA, ketika kedua register sedang dipertimbangkan, jalur sinyal clock dan sinyal data terletak di dalam FPGA. Dari artikel itu perlu untuk memperoleh pemahaman tentang konsep logika sinkron sebagai jaringan yang dijalin dari banyak transfer antar-register (Gbr. 1), dan istilah "kendur" (Gbr. 2).

Pada artikel ini, kami akan mempertimbangkan kasus transfer data, di mana salah satu dari dua register transfer berada di luar FPGA - ini adalah register perangkat eksternal - mikrokontroler, ADC, dll.

Angka: 1. Skema transfer data antar register dari register sumber (sumber) ke register tujuan (tujuan).

Angka: 2. Arti dari slacks relatif terhadap bagian depan capture pada input register penerima.

Rumus umum untuk menghitung slacks, diturunkan dari artikel sebelumnya:

minSetupSlSebuahck=minDSebuahtSebuahRequsayared-maksDSebuahtSebuahSEBUAHrrsayavSebuahl=

=SR+mintCLKtoDST−maxtCLKtoSRC−maxtSU−maxtCO−maxtD

minHoldSlack=minDataArrival−maxDataRequired=

=−HR+mintCLKtoSRC−maxtCLKtoDST+mintCO−maxtH+mintD

Mari kita bahas persyaratannya.

Slack adalah margin waktu. Itu harus positif.

Waktu preset (waktu penyetelan,tSU) - waktu minimum bahwa data harus sudah berada di input register penerima pada saat jam depan tiba di input jam penerima.

Tahan waktu (tahan waktu,tH) Adalah waktu minimum yang data masih harus ditahan di masukan penerima setelah depan jam tiba di masukan jam penerima.

Daftarkan waktu respons (waktu jam-ke-keluaran,tCO) Adalah waktu dari kedatangan jam depan ke masukan jam dari register sumber sampai munculnya data stabil baru pada keluarannya.

SR dan HR adalah Setup and Hold Relationship, perbedaan antara momen bagian depan pengambilan dan bagian depan pemicu pada sumber jam, dengan mempertimbangkan ketidakstabilan. Dalam kasus menganalisis transmisi FPGA internal, hanya tepi naik jam yang diambil, jadi ungkapan ini disederhanakan menjadiSR=T−CSU,HR=CHU... Tetapi antarmuka sering menggunakan front yang berbeda, jadi representasi yang lebih umum harus digunakan.

Preset / hold clock jitter (CSU / CHU) adalah ukuran clock jitter. Dalam kalkulasi, ini membawa arti dari margin "berjaga-jaga" untuk memperhitungkan fenomena yang disebabkan oleh frekuensi bekuan yang tidak sempurna.

tD Adalah waktu yang dibutuhkan sinyal data untuk melakukan perjalanan antar register.

tCLKtoSRCApakah waktu yang dibutuhkan tepi sinyal clock untuk melakukan perjalanan dari sumber clock ke input clock dari register sumber. Dan dari sumber jam ke register tujuan - masing - masingtCLKtoDST...

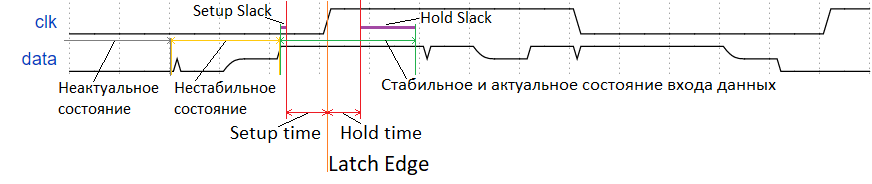

Jalur sinyal diilustrasikan pada Gambar 3.

Gambar. 3. Penunjukan waktu tempuh jalur sinyal jam dan data.

Dalam gambar ini, kita melihat dua titik - hijau dan merah. Keduanya adalah titik di mana jalur potongan sumber dan bagian penerima belum menyimpang. Titik hijau adalah keluaran dari buffer jam global, titik masuk ke jaringan jam global FPGA, relatif terhadap masukan jam dari semua register kira-kira berjarak sama. Titik merah adalah beberapa titik sembarang dalam jaringan jam global, di mana, seperti pada masukan jaringan, jam belum terpecah menjadi dua salinan dari dirinya sendiri, yang telah pergi ke register yang berbeda. Tetapi hanya titik hijau yang merupakan titik yang cocok untuk mulai menghitung waktu berlalunya jam, karena berada di salah satu tempat yang dapat dimengerti oleh penyusun. Dalam contoh ini, di input jaringan jam global. Namun dalam kasus antarmuka sederhana yang dicatat dari luar, titik hijau bisa jadi hanya kaki FPGA.Kompilator mengetahui pengaturan waktu dari titik ini ke setiap register. Dan titik merah, tempat di mana jalur dari dua jam yang dianalisis secara tidak sengaja bertepatan, tidak cocok untuk titik awal.

Jenis transmisi yang dianalisis

Mari mengklasifikasikan kasus untuk analisis temporal. Analisis dilakukan secara terpisah untuk setiap kaki FPGA sehubungan dengan blok tertentu. Sebagai hasil dari analisis, kemampuan kaki untuk mengirim atau menerima data dengan benar dinilai. Antarmuka eksternal untuk pertukaran data sinkron antara FPGA dan perangkat eksternal terdiri dari beberapa jalur yang terhubung ke kaki. Dari jumlah tersebut, satu baris adalah garis rusak. Itu harus dibagi antara register di kedua sisi. Garis yang tersisa, satu atau banyak, adalah jalur input atau output searah. Yang dimaksud dengan jalur input untuk FPGA adalah jalur output untuk perangkat eksternal, dan sebaliknya. Dalam artikel ini, kami hanya mempertimbangkan kasus analisis temporal yang paling sederhana, jadi kami tidak menyentuh antarmuka asinkron dan waktu otomatis, serta penggunaan jalur I / O dua arah.

Kasus analisis dapat diklasifikasikan menurut arah data relatif terhadap FPGA (Input / Output) dan arah jam relatif terhadap FPGA (data dihitung dari FPGA / dari sumber eksternal). Untuk setiap kasus, ada dua jenis analisis (Setup / Hold). Secara total, empat kasus untuk analisis dan delapan persamaan yang perlu kita turunkan.

Mengeluarkan data yang dihitung oleh jam FPGA internal

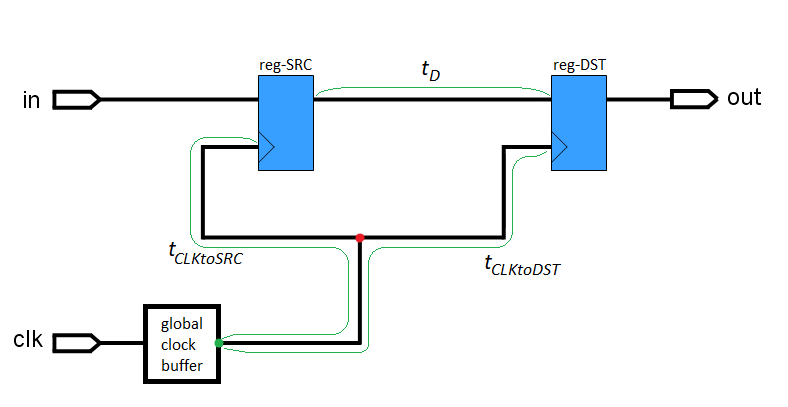

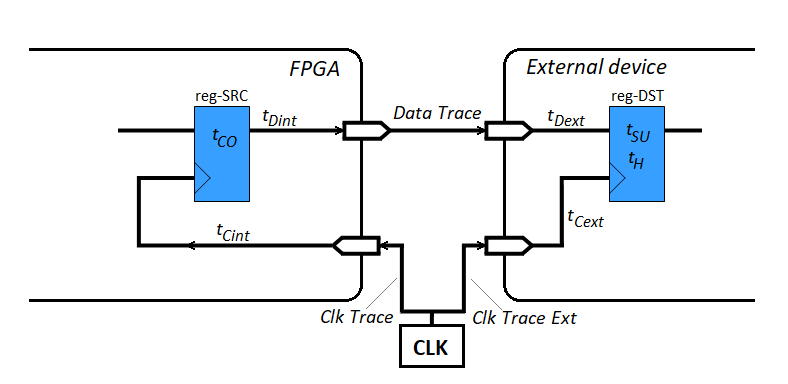

Pertimbangkan kasus ketika kita perlu memberikan sesuatu pada bagian kita yang rusak (Gbr. 4).

Skema transfer data dasar tidak berubah. Tetapi register sekarang milik dua sirkuit mikro yang berbeda, dan jalur data di antara mereka bukanlah logika kombinasional, tetapi hanya trek di papan tulis. Dan tugas kita adalah mengadaptasi rumus slack yang diketahui ke situasi yang sedikit berbeda.

Angka: 4. Mentransfer data ke luar pada jam FPGA Anda sendiri.

Pada Gambar 4, kita melihat skema transfer antar register. Ini menunjukkan waktu proses yang terkait dengan masing-masing register, dan waktu di mana sinyal menempuh jalur.

Saya mengatur pengindeksan berikut: waktu yang mengacu pada data ditandai dengan huruf D. Waktu yang mengacu pada jam ditandai dengan huruf C. Jika suatu peristiwa terjadi di dalam FPGA, maka waktunya ditandai dengan indeks "int", dan jika di perangkat eksternal, maka "ext" ... Waktu yang dibutuhkan untuk perjalanan potongan dari sumber potongan ke batang keluar potongan memiliki indeks terpanjang "Cintout". DataTrace dan ClkTrace adalah waktu tempuh dari jejak yang sesuai pada PCB. Blok "CLK" melambangkan semacam sumber internal jam.

Ciri utama dari besaran yang disebutkan dalam gambar adalah semuanya positif. Semuanya sama dengan durasi absolut dari setiap proses fisik, yang berarti secara fisik hanya dapat berupa nilai positif. Ini penting untuk penalaran lebih lanjut.

Sekarang kita akan melihat lebih dekat pada analisis kelonggaran preset. Melihat Gambar 4, kita dapat dengan mudah menghubungkan nilai yang diamati dengan istilah rumus slack:

Sekarang mari kita gantikan persamaan ini ke dalam rumus slack preset:tCLKtoSRC=tCint

tD=tDint+DataTrace+tDext

tCLKtoDST=tCintout+ClkTrace+tCext

minSetupSlack=minDataRequired−maxDataArrival=

=SR+mintCLKtoDST−maxtCLKtoSRC−maxtSU−maxtCO−maxtD=

=SR+min(tCintout+ClkTrace+tCext)−max(tCint)−tSU−tCO−

−max(tDint+DataTrace+tDext)

Sekarang kita menggunakan pengetahuan bahwa semua suku dalam tanda kurung lebih besar dari nol. Jadi kita tahu cara membuka tanda kurung seperti itu: jumlah minimum sama dengan jumlah minimum, dan jumlah maksimum sama dengan jumlah maksimum:

minSetupSlack=SR+mintCintout+minClkTrace+mintCext−maxtCint−

−tSU−tCO−maxtDint−maxDataTrace−maxtDext

Sekarang mari kita mengatur ulang istilah di beberapa tempat untuk mengelompokkan ketentuan proses di dalam FPGA dan proses di dalam perangkat eksternal dalam tanda kurung:

minSetupSlack=SR−(maxtCint+tCO+maxtDint−mintCintout)+

+minClkTrace−maxDataTrace−(maxtDext+tSU−mintCext)

Apa yang kita lihat dalam tanda kurung? Jika Anda melihat lebih dekat dan sekali lagi ingat bahwa semua nilai yang ditunjukkan lebih besar dari nol, maka kita dapat mengatakan bahwa kita melihat ekspresi waktu respons ekivalen tertentu (dengan tanda bintang) dari register FPGA dan waktu presetting ekuivalen dari register perangkat eksternal:

maxtCint+tCO+maxtDint−mintCintout=maxt∗CO

maxtDext+tSU−mintCext=maxt∗SU

minSetupSlack=SR−maxt∗CO+minClkTrace−maxDataTrace−maxt∗SU

Mengapa kita tidak menggunakan nilai yang setara jika produsen chip telah menghitungnya untuk kita, dengan mempertimbangkan penundaan internal mereka? Nilai yang setara di sisi FPGA akan dihitung oleh penyusun tanpa campur tangan pengguna, dan nilai yang setara dari perangkat eksternal secara eksplisit ditunjukkan dalam lembar data untuk perangkat tersebut.

Sekarang mari kita lihat lebih dekat ekspresi terakhir. Di dalamnya, tiga istilah pertama sudah diketahui penganalisis, karena kami telah menunjukkan frekuensi operasi dan besarnya ketidakstabilan. Kompilator telah melacak dan penganalisis mengetahui waktu respons yang setara dari registernya. Ini berarti penganalisis mengetahui durasi semua proses di dalam FPGA. Tetapi tiga istilah terakhir adalah unik untuk setiap kaki dan pengguna perlu menghitungnya sendiri dan menunjukkan kepada penganalisis sebagai angka. Nomor apa ini? Melihat lebih dekat pada tiga istilah terakhir, kita akan melihat bahwa mereka dapat diartikan sebagai maksimum negatif dari nilai tertentu:

minClkTrace−maxDataTrace−maxt∗SU=−maxOutputDelay

Dan nilai ini secara bermakna sama dengan penundaan dari segala sesuatu yang terjadi di luar FPGA, relatif terhadap segala sesuatu yang terjadi di dalam. Ini disebut bahwa - penundaan keluaran, Penundaan Output.

Mari kita rangkum:

minSetupSlack=SR−maxt∗CO−maxOutputDelay

maxOutputDelay=maxDataTrace+maxt∗SU−minClkTrace=

=max(DataTrace+t∗SU−ClkTrace)

Sekarang kita akan mendapatkan persamaan serupa untuk retention slack. Ingat kembali persamaan umum dan gantikan suku baru ke dalamnya:

Mari kita buka tanda kurung dan segera kelompokkan istilah-istilah di sekitar masing-masing register:minHoldSlack=minDataArrival−maxDataRequired=

=−HR+mintCLKtoSRC−maxtCLKtoDST+mintCO−maxtH+mintD=

=−HR+min(tCint)−max(tCintout+ClkTrace+tCext)+tCO−tH+

+min(tDint+DataTrace+tDext)

Dan sekali lagi kita melihat bagaimana suku-suku tersebut dikelompokkan ke dalam jumlah yang setara, kali ini tCO dan tH:minHoldSlack=−HR+(tCO+mintCint+mintDint−maxtCintout)−

−maxClkTrace+minDataTrace−(tH−mintDext+maxtCext)

Dan tiga istilah terakhir dapat dipahami sebagai penundaan eksternal minimum:minHoldSlack=−HR+mint∗CO+minDataTrace−maxClkTrace−maxt∗H

minDataTrace−maxClkTrace−maxt∗H=minOutputDelay

Mari kita rangkum:

minHoldSlack=−HR+mint∗CO+minOutputDelay

minOutputDelay=min(DataTrace−ClkTrace−t∗H)

Harus ditekankan itu minOutputDelay dan maxOutputDelay- ini adalah nilai minimum dan maksimum yang tidak sepenuhnya sama. Setiap analisis prasetel dan analisis retensi mempertimbangkan situasi yang berbeda dan penundaan eksternal yang berbeda. Ini berarti bahwa suku-suku tersebut, seperti dapat dilihat dari rumus-rumusnya, diambil secara berbeda.

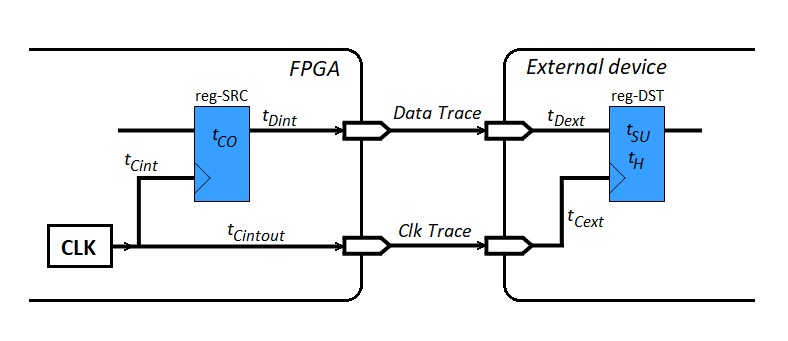

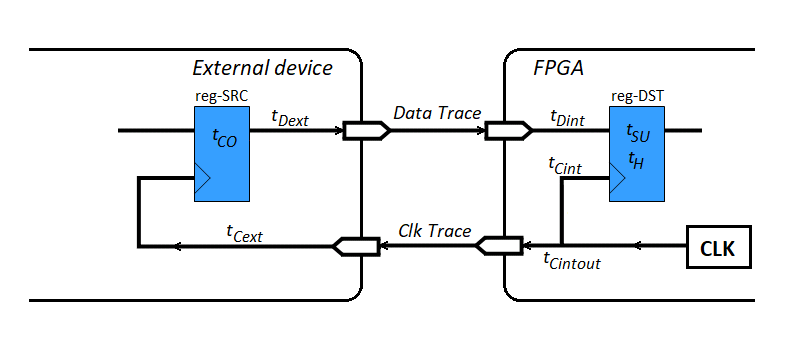

Mengeluarkan data yang dihitung berdasarkan jam eksternal

Sekarang mari kita beralih ke kasus ketika kita perlu memberikan sesuatu ke luar, tetapi menurut jam di luar FPGA (Gbr. 5). Secara umum, sumber jam terletak di luar FPGA, khususnya, dapat di dalam perangkat eksternal.

Angka: 5. Mentransfer data ke luar melalui jam eksternal.

Pada Gambar 5, kita melihat sumber potongan di luar. Dengan demikian, kuantitasnyatCintoutdan waktu untuk perjalanan potongan ke perangkat eksternal "Clk Trace Ext" muncul.

Melihat Gambar 5, kami menghubungkan nilai-nilai yang diamati dengan istilah rumus slack umum:

tCLKtoSRC=ClkTrace+tCint

tD=tDint+DataTrace+tDext

tCLKtoDST=ClkTraceExt+tCext

Dengan menggunakan ekspresi ini, kita akan membuka istilah dalam rumus slack preset, segera mengelompokkannya dengan register dan mendapatkan bentuk yang setara:

minSetupSlack=minDataRequired−maxDataArrival=

=SR+mintCLKtoDST−maxtCLKtoSRC−maxtSU−maxtCO−maxtD=

=SR−(maxtCint+tCO+maxtDint)−maxDataTrace−

−(maxtDext+tSU−mintCext)−maxClkTrace+minClkTraceExt=

=SR−maxt∗CO−max(t∗SU+DataTrace+ClkTrace−ClkTraceExt)

minSetupSlack=SR−maxt∗CO−maxOutputDelay

maxOutputDelay=max(t∗SU+DataTrace+ClkTrace−ClkTraceExt)

Kami mengurai kelonggaran retensi dengan cara yang sama:

minHoldSlack=minDataArrival−maxDataRequired=

=−HR+mintCLKtoSRC−maxtCLKtoDST+mintCO−maxtH+mintD=

=−HR+(mintCint+tCO+mintDint)+minDataTrace+minClkTrace−

−(tH−mintDext+maxtCext)−maxClkTraceExt=

=−HR+mint∗CO+minDataTrace+minClkTrace−maxClkTraceExt−maxt∗H

minHoldSlack=−HR+mint∗CO+minOutputDelay

minOutputDelay=min(DataTrace+ClkTrace−ClkTraceExt−t∗H)

Jika dalam skema ini kita mempertimbangkan kasus tertentu (tetapi sering), ketika sumber trik berada di dalam perangkat eksternal, maka rumus turunan hanya akan berubah dengan fakta bahwa ClkTraceExt menjadi sama dengan nol di dalamnya. Memindahkan sumber jam ke dalam perangkat eksternal akan menyebabkan dalam perhitungan kami penyebaran mikroskopis dari bekuan di dalam perangkat eksternal antara keluaran jam dan register, tetapi itu akan diperhitungkan oleh pabrikan perangkat eksternal dan akan dimasukkan dalam nilai yang setara.t∗SU dan t∗H...

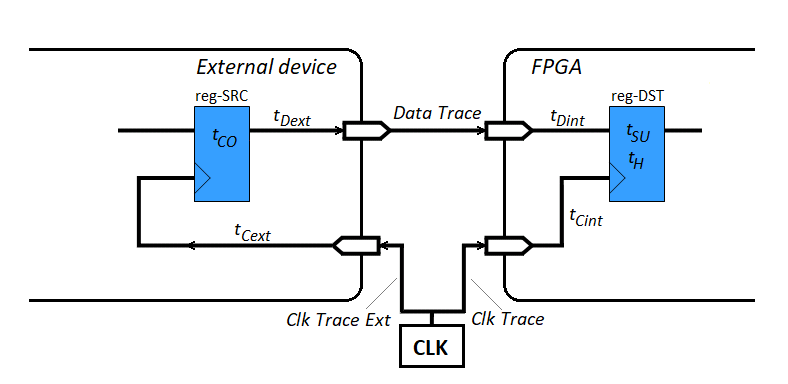

Input data clock oleh jam FPGA internal

Sekarang kita beralih ke pertimbangan kaki input dari antarmuka sinkron. FPGA dan perangkat eksternal pada Gambar 6 ditukar.

Angka: 6. Menerima data pada jam FPGA Anda sendiri.

Analisis skema semacam itu tidak lebih rumit dari yang sebelumnya.

Kami mengungkapkan, kami mengelompokkan ...tCLKtoSRC=tCintout+ClkTrace+tCext

tD=tDext+DataTrace+tDint

tCLKtoDST=tCint

Dan kami mendapatkan nilai penundaan eksternal, yang kali ini kami akan memanggil input:minSetupSlack=minDataRequired−maxDataArrival=

=SR+mintCLKtoDST−maxtCLKtoSRC−maxtSU−maxtCO−maxtD=

=SR−(tSU+maxtDint−mintCint+maxtCintout)−maxDataTrace−

−(tCO+maxtDext+maxtCext)−maxClkTrace

minSetupSlack=SR−maxt∗SU−maxInputDelay

maxInputDelay=max(DataTrace+t∗CO+ClkTrace)

Sekarang pegangannya kendur:

minHoldSlack=minDataArrival−maxDataRequired=

=−HR+mintCLKtoSRC−maxtCLKtoDST+mintCO−maxtH+mintD=

=−HR−(tH−mintDint+maxtCint−mintCintout)+minDataTrace+

+(tCO+mintDext+mintCext)+minClkTrace

minHoldSlack=HR−maxt∗H+minInputDelay

minInputDelay=min(t∗CO+DataTrace+ClkTrace)

Memasukkan data yang dihitung berdasarkan jam eksternal

Juga, menurut knurled, kami melihat skema transfer data dan mengungkapkan ketentuan rumus umum.

Angka: 7. Penerimaan data pada jam eksternal.

tCLKtoSRC=ClkTraceExt+tCext

tD=tDext+DataTrace+tDint

tCLKtoDST=ClkTrace+tCint

Formula slack preset:

minSetupSlack=minDataRequired−maxDataArrival=

=SR+mintCLKtoDST−maxtCLKtoSRC−maxtSU−maxtCO−maxtD=

=SR−(tSU+maxtDint−mintCint)−maxDataTrace−

−(tCO+maxtDext+maxtCext)−maxClkTraceExt+minClkTrace=

=SR−maxt∗SU−max(t∗CO+DataTrace+ClkTraceExt−ClkTrace)

minSetupSlack=SR−maxt∗SU−maxInputDelay

maxInputDelay=max(t∗CO+DataTrace+ClkTraceExt−ClkTrace)

Rumus retensi kendur:

minHoldSlack=minDataArrival−maxDataRequired=

=−HR+mintCLKtoSRC−maxtCLKtoDST+mintCO−maxtH+mintD=

=−HR−(tH−mintDint+maxtCint)+minDataTrace+

+(tCO+mintDext+mintCext)+minClkTraceExt−maxClkTrace

minHoldSlack=−HR−maxt∗H+minInputDelay

minInputDelay=min(t∗CO+DataTrace+ClkTraceExt−ClkTrace)

Sekali lagi, jika sumber jam ada di dalam perangkat eksternal, maka kita cukup menyamakan ClkTraceExt dengan nol.

Interpretasi visual

Rumus memang bagus, tetapi jika Anda mendalami topik ini untuk pertama kalinya, maka rumus tersebut terlihat tidak bisa dipahami, tidak hidup. Saya ingin sesuatu yang lebih jelas sehingga rumus mendapatkan makna yang terlihat. Oke, mari kita analisis arti fisik dari rumus-rumus tersebut, dengan mengambil, misalnya, kasus keluaran data oleh jam eksternal . Izinkan saya mengingatkan Anda bagaimana diagram dan rumusnya terlihat:

Gbr. 8. Transfer data ke luar melalui jam eksternal.

minSetupSlack=minDataRequired−maxDataArrival=

=SR−maxt∗CO−maxt∗SU−maxDataTrace−maxClkTrace+minClkTraceExt

minHoldSlack=minDataArrival−maxDataRequired=

=−HR+mint∗CO+minDataTrace+minClkTrace−maxClkTraceExt−maxt∗H

Selama transfer data, dua peristiwa terjadi: register sumber menyala dan register tujuan menyala. Peristiwa terjadi karena dipicu oleh front clok yang muncul dari sumber cloc. Dari sini kita akan mulai mencari.

Sumber jam menghasilkan bagian depan start-up dan sampai ke FPGA selama ClkTrace. Kemudian register FPGA dipicu selamat∗CO... Selanjutnya, data baru yang dihasilkan oleh operasi ini berpindah dari FPGA ke perangkat eksternal selama DataTrace.

Di sisi lain, sumber jam juga menghasilkan bagian depan pengambilan, yang sampai ke perangkat eksternal selama ClkTraceExt.

Kedua peristiwa ini terjadi pada input data dari perangkat eksternal. Dan di sini penting bahwa data tiba di sana sebelum register penerima mulai menangkap. Mereka harus datang dengan setidaknya beberapa waktu tersisa.t∗SU, atau lebih baik lagi. Kasus terburuk dianggap untuk memastikan ini benar. Jika ada cadangan bahkan dalam kasus terburuk, maka semuanya pasti beres. Oleh karena itu, momen terburuk kedatangan data adalah momen terbaru,max(ClkTrace+t∗CO+DataTrace)... Dan momen terburuk menunggu data adalah momen paling awal,minClkTraceExt−maxt∗SU... Dan bahkan dalam kasus terburuk, momen kedua harus lebih lambat dari yang pertama:

Semoga penjelasan ini lebih menjelaskan apa yang sedang terjadi.LatchEdge+minClkTraceExt−maxt∗SU>

>LaunchEdge+max(ClkTrace+t∗CO+DataTrace)

Dalam ungkapan ini, kita melihat momen di depan - LaunchEdge dan LatchEdge, yang biasanya tersembunyi dalam istilah SR dan HR. Mari kita ingat apa itu. Empat tepi dipertimbangkan dalam analisis prasetel dan penahanan:

Setup Launch Edge adalah tepi yang akan menyebabkan sumber mengirim data yang harus ditangkap oleh penerima.

Hold Launch Edge adalah bagian depan yang akan memaksa sumber untuk mengirim data berikutnya, yang dapat mencegah penerima mengambil data sebelumnya. Menurut definisi, selalu ada satu periode jam antara Setup LaunchEdge dan Hold Launch Edge.

Setup Latch Edge adalah bagian depan yang akan memaksa penerima untuk menangkap data masukan.

Hold Latch Edge adalah Setup Latch Edge yang sama. Faktanya, Latch Edge secara fisik adalah satu, hanya diberi dua nama untuk kecantikan dalam dua jenis analisis.

Dalam FPGA, logika sinkron biasanya hanya berfungsi pada tepi yang naik (Gambar 9). Dalam kasus ini, dari sudut pandang analisis kendur, preset Setup Launch Edge dan Setup Latch Edge diberi jarak satu sama lain dengan satu periode jam, dan dari sudut pandang analisis holding, Hold Launch Edge dan Hold Latch Edge bertepatan.

Angka: 9. Saling mengatur tepi dalam kasus ketika kedua register memiliki clock oleh tepi yang naik.

Namun, tidak ada yang melarang menempatkan sinyal clock terbalik pada input clock dari salah satu dari dua register dan dengan demikian membuatnya bekerja di tepi jatuh jam. Omong-omong, ini sering dilakukan di antarmuka SPI yang sama. Mari kita lihat lebih dekat opsi ini.

Mari kita pertimbangkan situasi keluaran data dari FPGA oleh jam eksternal, tetapi salah satu dari dua register beroperasi pada jam terbalik, yaitu di sepanjang tepi jatuh. Biarkan itu menjadi register penerimaan pada perangkat eksternal. Kemudian peran garis depan dalam waktu akan didistribusikan secara berbeda (Gbr. 10).

Angka: 10. Saling pengaturan front dalam kasus ketika sumber clock oleh tepi naik, dan penerima oleh tepi jatuh.

Pencantuman register ini memungkinkan Anda untuk menyelaraskan ukuran slacks untuk preset dan hold. Jika register bekerja dari depan ke arah yang sama, maka karena sedikitnya, dibandingkan dengan periode jam, propagasi sinyal di sepanjang jalur papan, kelonggaran preset akan sangat besar, dan kelonggaran penahan akan sangat kecil.

Gambar 11 menunjukkan waktu jam pada sumber jam. Untuk menyederhanakan gambar, saya tidak menentukan istilah ClkTraceExt. Kami akan berasumsi bahwa sumber kerusakan ada di dalam perangkat eksternal.

Angka: 11. Posisi dari slacks dalam waktu relatif terhadap bagian depan jam dalam kasus ketika penerima diberi jam oleh sisi jatuh.

Dalam gambar ini, Kedatangan Data maks- ini adalah momen terakhir ketika data dapat sampai di masukan penerima. Saat paling awal ketika data seharusnya sudah ada di input penerima adalah min Data Diperlukan . Saat terakhir ketika data masih perlu di input penerima adalah Max Data Diperlukan . Dan momen paling awal ketika data sudah dapat meninggalkan input penerima, digantikan oleh data berikutnya, disebut min Data Leaving .

Sekarang rumus dan suku-suku mereka akan menjadi lebih jelas.

Cara menggunakan rumus yang dihasilkan

Kami telah memperoleh rumus untuk penundaan eksternal dan dapat menghitung jumlah penundaan tertentu agar sesuai dengan file batasan waktu. Secara global, rumus ini terdiri dari dua jenis istilah - karakteristik pengaturan waktu port perangkat eksternal dan latensi pada jalur papan.

Spesifikasi port biasanya ditemukan dalam lembar data di bawah bagian berjudul seperti "Karakteristik Listrik / Spesifikasi AC / Persyaratan Waktu". Terkadang ciri-ciri ini disebut dengan nama yang berbeda dan Anda harus pintar-pintar menemukannya. Tetapi tabel dengan angka biasanya disertai dengan grafik waktu yang memungkinkan Anda untuk mengidentifikasi parameter yang Anda inginkan. Nuansa penting, yang dapat membingungkan, dalam lembar data untuk banyak sirkuit mikro, pin output sering dijelaskan oleh parameter "Setup Output time" dan "Hold Output time". Dalam rumus artikel ini, mereka harus dibandingkan sebagai berikut:tSUO=maxt∗CO,tHO=mint∗CO...

Dengan trek, ini sedikit lebih rumit. Perhitungan yang tepat dari latensi di papan tulis bukanlah pertanyaan yang sepele. Penundaan tergantung pada panjang, lebar, ketebalan dan sudut trek, ketebalan dan bahan papan, jarak ke berbagai lapisan tanah, kedekatan jalur satu sama lain, dan banyak faktor lainnya. Namun, pengaruh dari masing-masing faktor ini agak kecil dan pada frekuensi antarmuka rendah, hingga puluhan megahertz, kesulitan ini dapat diabaikan. Perhitungan yang disederhanakan dari penundaan lintasan terlihat seperti ini: kecepatan rambat gelombang dalam kertas timah dianggap sama dengan setengah kecepatan cahaya dalam ruang hampa. Ketika dikonversi, ini menghasilkan sekitar 0,007 ns / mm. Kesalahan perkiraan ini diimbangi dengan berbagai perkiraan penundaan. Untuk penundaan maksimum, kami menganggap penundaan spesifik sama dengan 0,010 ns / mm, dan untuk minimum - 0,005 ns / mm.

Ada satu nuansa lagi. Insinyur sirkuit, ketika merancang papan sirkuit tercetak, mencoba meregangkan jalur antarmuka sinkron dengan cara yang kira-kira sama dan menjaga panjangnya tetap sama. Periksa data dan panjang track jam pada papan target Anda. Kemungkinan besar mereka hampir sama dan komponen ekspresi (DataTrace - ClkTrace) dalam praktiknya dapat dianggap nol.

Jika ada elemen di jalur data atau potongan yang menyebabkan penundaan, itu juga harus diperhitungkan. Ini bisa berupa penyangga, inverter, konverter level atau isolasi galvanik. Unsur-unsur tersebut mampu menimbulkan penundaan yang sangat besar, puluhan nanodetik, sehingga perlu diperlakukan dengan sangat hati-hati.

Kesimpulan

Di artikel ini, Anda melihat rumus yang menentukan pelaksanaan batasan waktu di antarmuka sinkron. Mengetahui rumus ini, Anda dapat memahami pada apa transfer data yang berhasil bergantung dan bagaimana menghitung batas yang benar untuk penganalisis. Pada artikel selanjutnya saya akan memberikan contoh format file batasan waktu dan menggunakan analyzer.