Artikel ini dibuat berdasarkan pengalaman saya sendiri dalam upaya untuk menjelaskan topik ini kepada diri saya sendiri, siswa-siswa dan kolega yang ingin tahu agar tidak terjun ke dalam hutan akademis yang musykil, tetapi sesederhana dan setransparan mungkin, dalam bahasa sehari-hari. Saya belajar untuk bekerja dengan FPGA tanpa belajar dan pelatihan tentang topik ini, dan saya tahu dari pengalaman saya sendiri betapa sulitnya untuk memahami sesuatu tanpa dasar teoritis dalam topik ini dan dalam sirkuit. Bagi peternak berpengalaman, di atas masih SD. Tetapi untuk beberapa siswa tahun keempat, artikel ini akan berguna dan akan membantu untuk memahami semua kelonggaran, pengaturan dan penahanan ini.

Dalam artikel ini, saya akan menggunakan istilah dengan duplikasi versi bahasa Inggrisnya dalam tanda kurung. Ini dilakukan karena terminologi yang bersatu tidak diselesaikan, dan dengan duplikasi lebih mudah untuk memahami konsep apa yang sedang dibahas dan, jika perlu, mencari informasi tentangnya dalam sumber-sumber berbahasa Inggris.

pengantar

Saya akan memberikan pengantar singkat dalam bahasa konsep sederhana.

Agar sesuatu dapat bekerja di FPGA, Anda perlu memuat (mengunggah, menjahit) file firmware ke dalamnya, menggunakan pemrogram dan utilitas firmware. File firmware adalah produk kompilasi CAD dari proyek tertentu - folder dengan file, yang masing-masing menjelaskan beberapa aspek proyek. Dalam kasus sederhana, pengguna sendiri hanya menjelaskan file dengan kode sumber, file dengan pinout, dan file dengan batasan waktu. Sisa file ditangani secara diam-diam oleh CAD. Dari tiga serangkai ini, hanya file batasan waktu yang secara formal opsional.bagian dari proyek. Sebenarnya, jika proyek Anda tidak berisi frekuensi yang lebih tinggi dari 30-50 MHz, kemungkinan besar proyek tersebut akan dapat bekerja tanpa file ini. Opsi ini sesuai untuk kemudahan membuat proyek pendidikan pertama. Namun, jika proyek pelatihan Anda sudah berisi frekuensi jam tinggi dan tidak dilengkapi dengan file batasan waktu, kemungkinan besar di suatu tempat di dalam FPGA, pemrosesan data akan terganggu, dan Anda tidak akan dapat menemukan titik mana dalam proyek tersebut. Adapun untuk bekerja, bukan belajar, deskripsi file lengkap pembatasan sangat diperlukan . Merupakan tanggung jawab Anda untuk memverifikasi dan memvalidasi fungsionalitas proyek Anda.

Kompilator menempatkan proyek Anda pada chip FPGA, menerima file koneksi dari semua elemen fisik. Penganalisis waktu menggunakan file koneksi untuk menghitung semua durasi transfer data ke FPGA. Durasi ini tidak boleh terlalu lama atau terlalu pendek. File batasan waktu memberi tahu penganalisis dalam kerangka apa durasi ini seharusnya. Dengan menggunakan hasil analisis waktu, pengembang dapat melihat di bagian mana dari proyek ada margin waktu, dan karena itu dalam frekuensi, dan di mana tidak ada margin tersebut.

Sistem sinkron menyinkronkan data pengolahan bekerja menggunakan sinyal sinkronisasi jam, yang dalam jargon yang lama disebut sebagai jam dari Inggris jam... Hasil operasi antara disimpan dalam register yang mampu mengingat status pada input pada saat kedatangan tepi sinyal clock dan menahannya pada output hingga siklus clock berikutnya.

Jadi, sirkuit sinkron terdiri dari transfer data antar register ( RTL, logika transfer register, transfer r2r ). Dan aspek kunci dari analisis temporal terdiri dari mengukur Slack ( kendur ). Kata ini secara harfiah diterjemahkan sebagai "cadangan waktu", "kendur", tetapi dalam lingkungan berbahasa Rusia, kertas kalkir dari bahasa Inggris sering digunakan - "kendur". Dalam transfer antar registrasi, kita berbicara tentang slacks preset ( Setup ) dan hold slacks ( Hold ).

Transfer antar register

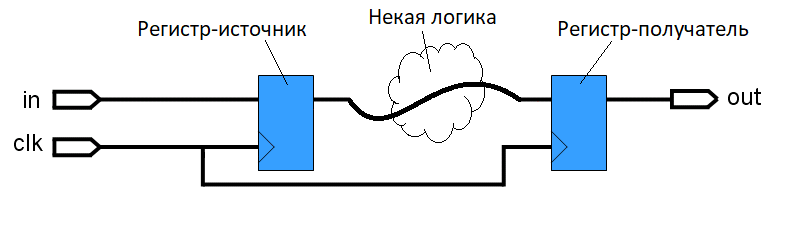

Transfer antar register (Gbr. 1) dianggap sebagai sistem dari dua register yang terhubung secara berurutan yang beroperasi pada jam sinkron dalam kasus umum. Dalam kasus sederhana, di satu bagian. Satu register berperan sebagai sumber (source), dan yang lainnya berperan sebagai penerima data (tujuan). Dan pada transfer antar register berikutnya, register penerima ini sudah dianggap sebagai sumber, dll. Di antara register di jalur data ada beberapa logika kombinasional yang ditentukan pengguna. Ini asinkron karena tidak memiliki elemen memori dengan sinyal sinkronisasi, seperti register. Logika ini adalah perilaku itu, operasi logis yang dijelaskan pengguna dengan kodenya. Register adalah "variabel" satu-bit yang diberi nama oleh pengguna dalam kode dan beroperasi secara terpisah,atau menggabungkan menjadi vektor dan array.

Angka: 1. Skema transfer data dari register ke register

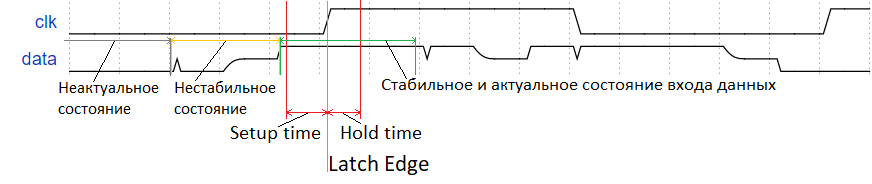

Ada dua konsep yang terkait dengan penerimaan data oleh register penerima: waktu Setup dan interval waktu Hold. Mereka menguraikan rentang waktu di mana sinyal di masukan penerima harus stabil dan relevan. Stabil - pada dasarnya berarti tegangannya harus sangat dekat dengan salah satu dari dua status logis - "0" atau "1", dan tidak menjuntai di antara keduanya dengan kemungkinan kebingungan. Relevan - artinya bahwa bit informasi ini dalam maknanya harus berhubungan dengan detak jam yang akan menangkapnya, dan bukan sedikit terlambat dari detak sebelumnya.

Waktu penyetelan - waktu prasetel, waktu minimum yang sebelum kedatangan jam depan sinyal data harus sudah disetel ke keadaan stabil.

Hold time - waktu tunggu, waktu minimum setelah datangnya jam depan, sinyal data harus tetap ditahan dalam keadaan stabil.

Artinya, data di masukan penerima harus stabil dan mutakhir tidak hanya pada saat kedatangan jam depan, tetapi juga selama interval waktu perlindungan tertentu di sekitarnya (Gbr. 2), dengan durasi setidaknya Setup_time + Hold_time. Jika kondisi stabilitas data terpenuhi selama interval ini, register pasti dapat menangkap data yang masuk tanpa kesalahan, jika tidak, tidak ada yang menjamin bahwa tidak akan ada kegagalan.

Angka: 2. Atur Waktu dan Tahan waktu sebagai interval penjaga di sekitar tepi tangkap pada input jam dari register

Nilai waktu penataan dan waktu penahanan ditentukan secara ketat oleh pabrikan FPGA. Mereka bergantung pada teknologi produksi kristal dan dianggap sebagai konstanta untuk analisis, sama untuk setiap register di kristal. Bagaimanapun, nilai-nilai ini tidak bergantung pada pengguna dengan cara apa pun; akuntansi mereka adalah tugas hanya untuk utilitas analisis waktu. Tidak penting bagi kita untuk mengetahui apa persamaan mereka, yang penting bagi kita hanya untuk mengetahui bahwa mereka ada dan tidak sama dengan nol.

Inti dari analisis waktu adalah untuk menghitung kelonggaran waktu untuk setiap pasangan register dalam proyek, di antaranya ada transfer data, bahwa data harus stabil selama interval penjaga. Ada banyak pasangan r2r dalam proyek ini, ribuan, atau bahkan jutaan, tetapi masing-masing harus dianalisis untuk memastikan bahwa proyek tersebut berhasil.

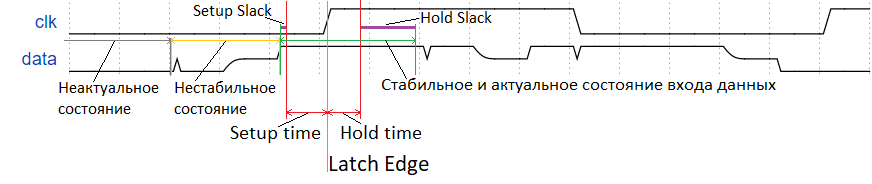

Ada juga dua slack, masing-masing - Setup Slack dan Hold Slack (Gbr. 3).

Setup Slack mencirikan margin waktu yang dimiliki data dari saat stabilisasi hingga awal interval waktu Setup.

Hold Slack mencirikan margin waktu yang dimiliki data dari akhir interval waktu Hold hingga hilangnya stabilitas oleh data.

Celana panjang harus positif. Jika slack negatif, maka kondisi kestabilan data masukan tidak terpenuhi dan data akan berdetak. Semakin banyak slack, semakin baik, tetapi Anda perlu memahami bahwa pada setiap register-tujuan, slack preset dan hold memiliki satu waktu yang sama untuk dua. Ini berarti bahwa peningkatan satu kelonggaran selalu menyebabkan penurunan kelonggaran lainnya. Oleh karena itu, opsi terbaik adalah ketika kedua slack bernilai positif dan kira-kira sama satu sama lain, mis. keseimbangan celana panjang dihormati.

Angka: 3. Positif slacks, syarat penerimaan data yang sukses terpenuhi, tetapi tidak ada keseimbangan antara slack

Perhitungan kendur

Sekarang mari kita lanjutkan ke cara menghitung celana panjang ini. Mari kita mulai dengan Setup Slack.

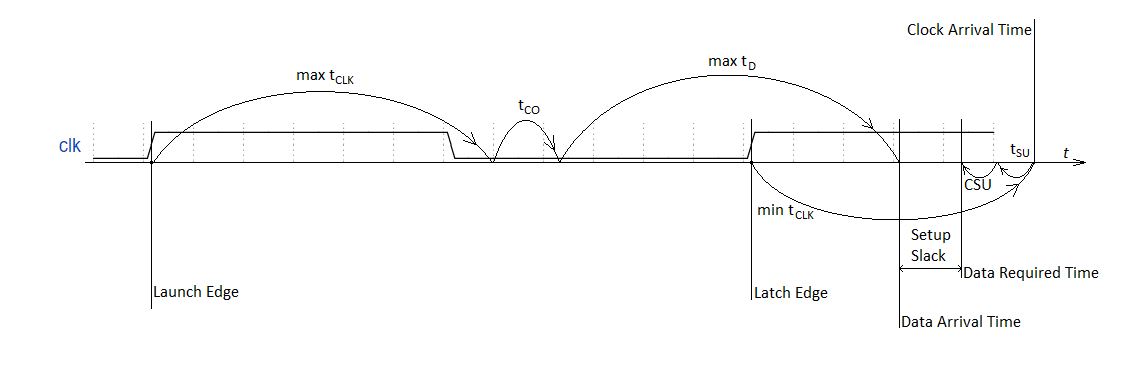

Pertimbangkan skema transfer data pada Gambar. 4.

Gambar. 4. Skema transfer data

Di sini kami memperkenalkan konsep seperti trigger front, capture front, data arrival time, data waiting time dan clock arrival time.

The Launch Ujung adalah depan jam yang datang ke input dari register sumber dan memulai proses transfer data.

The Latch Ujung adalah depan jam yang tiba di penerima mendaftar dan kekuatan untuk ambil data pada input.

Saat kedatangan data ( Data Arrival Time ) didefinisikan sebagai kedatangan data yang sebenarnya pada register penerima.

The data Diperlukan Waktu didefinisikan sebagai waktu yang dibutuhkan untuk data untuk mencapai tujuan sebelum waktu yang telah ditetapkan pada register tujuan.

Waktu kedatangan sebuah jam ( Clock Arrival Time ) diartikan sebagai waktu bagian tepi pengambilan dari input jam dari seluruh sirkuit ke input jam penerima. Selain itu, capture front berarti front berikutnya setelah front launch. Bagian depan peluncuran mengirimkan data dari sumber ke penerima, dan setelah satu periode jam, bagian depan pengambilan menangkap data ini di pihak penerima.

Input jam dari seluruh rangkaian dipahami sebagai satu titik dari mana jam menyimpang ke semua register yang beroperasi di dalamnya. Ini biasanya merupakan keluaran dari buffer jam global atau keluaran dari PLL. Dalam kasus yang paling primitif, ini adalah kaki FPGA, yang menghubungkan generator jam.

Istilah yang terlibat dalam analisis temporal mungkin tidak memiliki nilai titik, tetapi kisaran nilai yang mungkin, tergantung pada jejak desain dan suhu kristal. Oleh karena itu, kelonggaran terburuk dianalisis. Pertukaran data dianggap berhasil jika, bahkan dalam kondisi terburuk untuk kelonggaran, tetap positif.

Bagaimana saat kedatangan data berhubungan dengan tepi pemicu?

Kami menganggap kedatangan data melewati rantai dengan register dari beberapa peristiwa yang diprakarsai oleh tepi pemicu.

Bagian depan pemicu muncul pada input clock dari sistem, kemudian mencapai input register sumber untuk beberapa waktu, kemudian untuk beberapa waktu register ini dipicu dan mengirim data baru ke output, kemudian data ini melewati rangkaian logika kombinasional ke register penerima. Varian bagian data yang terburuk dan paling lambat dipertimbangkan, oleh karena itu istilah tersebut dilengkapi dengan awalan "maks".

Dalam rumus ini, istilah untuk tepi pemicu membawa arti titik referensi relatif terhadap peristiwa yang berkembang, dan bukan nilai yang diukur dalam nanodetik.

IstilahAdalah waktu maksimum yang diperlukan untuk tepi pemicu untuk beralih dari input jam dari seluruh rangkaian ke input jam dari sumber. Biasanya, penganalisis hanya mengambil rentang waktu dari "tepat tidak kurang dari" hingga "tepat tidak lebih dari" dan mengganti batas atas "pasti tidak lebih dari" ke dalam rumus ini. Nilai ini tidak bergantung pada pengguna. Kompiler itu sendiri memutuskan di mana menempatkan register pada kristal dan memperhitungkan waktu yang dibutuhkan jam untuk melakukan perjalanan ke sana. Jaringan koneksi di mana sinyal clock menyimpang dari buffer jam global ke register dirancang sedemikian rupa sehingga sinyal clock mencapai register mana pun dalam jumlah waktu yang hampir sama. Oleh karena itu, pada kenyataannya, perbedaan antara dan sangat kecil, tapi tetap diperhitungkan.

Istilah- ini adalah waktu clock-to-output , yang digunakan register untuk melihat bagian depan pada input clock mengubah data pada outputnya. Penganalisis menganggap nilai ini sama untuk semua register pada chip. Nilai ini tidak bergantung pada pengguna.

Istilah terakhirAdalah waktu maksimum untuk suatu peristiwa (data) melewati logika kombinasi antara register, yang ditentukan oleh pengguna. Nilai ini sangat bergantung pada pengguna. Ini mengungkapkan jumlah logika kombinasional antara register. Pada gilirannya, logika kombinasional rantai panjang seringkali merupakan hasil dari pengkodean yang tidak akurat oleh pengguna.

Saat pecahan tiba di penerima lebih mudah dihitung:

Ini adalah momen paling awal di mana tepi tangkap mencapai input jam dari register penerima.

Istilah- ini adalah waktu minimum di mana bagian depan pengambilan akan mencapai input jam penerima, yaitu, dengan analogi dengan rumus sebelumnya, kali ini "pasti tidak kurang dari". Tanda hubung dalam hal ini berarti kita berbicara tentang input jam penerima, bukan sumbernya.

Waktu tunggu untuk data didefinisikan sebagai waktu yang dibutuhkan data untuk sampai ke penerima sebelum waktu yang telah ditentukan pada register penerima:

Istilah - Ini sudah diketahui oleh kami Waktu penyiapan, yang dianggap sama untuk setiap register pada kristal. Kali ini tidak tergantung pada pengguna.

IstilahApakah Clock Setup Uncertainty , ketidakpastian waktu preset. Seperti ketidakpastian lainnya dalam analisis temporal CSU bukanlah proses fisik, tetapi cara untuk mencerminkan pengaruh jitter dalam analisis, atau hanya cara untuk memasukkan waktu jaga ke dalam analisis untuk berjaga-jaga. Dengan kata sederhana, ini adalah cadangan waktu untuk memperhitungkan proses yang sulit.

Sekarang istilah-istilah ini didefinisikan, kita dapat mendefinisikan kelonggaran prasetel sebagai perbedaan terkecil antara waktu yang diizinkan untuk melakukan perjalanan ke tujuan dan waktu yang sebenarnya dibutuhkan.

Sekarang mari kembangkan istilah-istilah ini dan atur ulang sedikit:

Istilah baru muncul di sini.

Jelas tentang periode, ini adalah periode frekuensi clock, mis. waktu antara Launch Edge dan Latch Edge.

Istilah- ini adalah clock skew - nilai minimum penyebaran waktu kedatangan dari satu tepi jam dari input jam sistem ke register sinkron yang berbeda. Penyebaran jam minimum didefinisikan sebagai perbedaan antara penundaan jam terkecil ke penerima dan penundaan jam terbesar ke sumber.... Penganalisis tidak membuat perbedaan dalam memperkirakan waktu ini untuk register yang berbeda pada sebuah chip.

Ini adalah cara kami menghitung kelonggaran preset. Margin positif bagus, margin negatif buruk. Slack secara harfiah berarti kendur. Jadi jika ada kelonggaran, maka transfer antar register tidak dikonfigurasi "vnatyag", "utas" bersyarat melorot dengan bebas. Slack negatif - ini berarti benang transmisi ditarik dan putus.

Gambar 5 menunjukkan bagaimana rumus slack dapat direpresentasikan secara grafis:

Gbr. 5. Representasi Grafis dari Setup Slack Expression

Ini menunjukkan hubungan di latar belakang sinyal clock, dan ini adalah sinyal clock pada input clock sistem, bukan pada input register manapun.

Sekarang mari kita hitung kelonggaran retensi dengan cara yang serupa .

Itu juga dapat diwakili oleh ekspresi di mana istilah-istilah telah berubah tanda:

Istilah-istilah ini sekarang dipertimbangkan dari sisi lain.

Sekarang varian tercepat dari bagian data dipertimbangkan di sini dan di mana "max" adalah "min".

Momen kedatangan bagian depan clok juga dilihat dengan cara yang berbeda, sebagai yang terbaru:

Penting untuk dicatat bahwa dalam kasus Hold Slack, bagian depan Launch Edge dan Latch Edge sekarang menjadi satu bagian depan yang sama, daripada dua bagian depan yang berbeda yang dipisahkan oleh periode jam. Register penerima dalam situasi ini perlu memiliki waktu untuk menyimpan data pada masukan selama waktu penahanan sejak kedatangan jam depan. Tetapi data diubah pada inputnya oleh front yang sama, yang datang ke tempat lain ke register sumber. Oleh karena itu, dalam analisis retention slack, terdapat perbedaansama dengan nol, bukan titik.

Waktu yang diperlukan dalam hal ini didefinisikan sebagai waktu di mana data tidak boleh berubah pada input data penerima, agar tidak menangkap waktu penahanan:

Istilah - ini sudah kita ketahui Tahan waktu, waktu penahanan. Ini dianggap sama untuk setiap register pada chip dan tidak bergantung pada pengguna.

IstilahApakah Jam Tahan Ketidakpastian , ketidakpastian waktu penahanan. Secara umum, ini memiliki arti yang sama dengan CSU, dan biasanya dianggap sama.

Jika, seperti dalam kasus kelonggaran prasetel, Anda memperluas istilah dan menukarnya, ekspresi kelonggaran retensi dapat diubah menjadi bentuk berikut:

Lihat lagi rumus ini

Di atas, disajikan metode untuk menghitung celana panjang, yang merupakan karakteristik pemahaman manusia tentang proses yang terjadi. Di sini "bagian depan akan datang ...", "data akan datang ...". Jika Anda tertarik, sebagai pelengkap, saya akan memberi tahu Anda bagaimana penganalisis batasan waktu membayangkan perhitungan ini.

Penganalisis mengelompokkan istilah secara berbeda, berdasarkan alasan mesinnya. Tapi pada akhirnya hasilnya sama.

Ini menggunakan istilah Clock Setup Relationship ( SR ) dan Clock Hold Relationship ( HR ) - yang dapat diterjemahkan sebagai rasio waktu antara tepi pemicu untuk preset dan tahan, masing-masing.

Gambar 6 menunjukkan bagaimana front-front ini terkait:

Gbr. 6. Bagian depan yang digunakan dalam perhitungan kendur.

Anda dapat segera mengubah ekspresi yang dihasilkan menjadi bentuk yang lebih mudah dipahami:

Waktu antar-register terlama (Diperlukan r2r Terbesar) adalah waktu maksimum yang tersedia bagi data untuk mencapai tujuan sebelum dimulainya interval preset:

Penundaan antar-register terpanjang (Delay r2r terpanjang) adalah waktu yang diperlukan untuk mentransfer data dari register sumber ke register tujuan di sepanjang jalur terpanjang:

Sekarang kita dapat mendefinisikan slack preset sebagai perbedaan antara waktu yang tersedia untuk mencapai register tujuan dan waktu sebenarnya untuk sampai ke sana:

Memperluas istilah rumus ini akan memberi kita representasi yang sudah dikenal dari kelonggaran prasetel:

Sekarang tentang kelonggaran retensi. Persyaratan r2r terkecil adalah waktu yang diperlukan untuk menyimpan data pada input register tujuan:

Penundaan antar-register terpendek:

Sekarang kita mendefinisikan kelonggaran preset sebagai perbedaan antara waktu tercepat untuk data meninggalkan masukan penerima dan waktu yang diperlukan untuk menyimpannya di sana:

Saat memperluas istilah, ekspresi tersebut juga mengambil bentuk yang sudah dikenal:

Kesimpulan apa yang bisa diambil dari rumus membosankan?

Kami telah melihat bagaimana celana panjang dihitung. Bagaimana cara menggunakan pengetahuan ini?

Mari kita lihat ekspresi kendur lagi:

Jika beberapa kelonggaran proyek menjadi negatif, maka kita dapat mengubahnya dengan mengubah persyaratannya. Artinya, kami melihat bagaimana kami dapat memperbaiki celana panjang yang buruk.

Kami melihat istilah yang tidak bergantung pada pengguna, tetapi hanya bergantung pada teknologi kristal. Itu... Tidak ada cara untuk ikut campur.

Kami melihat istilah CSU dan CHU, yang biasanya digunakan oleh penganalisis sama dengan parameter CU - Ketidakpastian Jam, ketidakstabilan frekuensi clock. Secara umum, parameter ini kecil, puluhan pikodetik. Ini ditentukan oleh pengguna di file pembatasan. Dan pengguna, pada gilirannya, mengambilnya dari spesifikasi generator jam. Dianggap bahwa buffer jam atau PLL FPGA internal, yang menerima jam eksternal dari osilator dan mengubahnya menjadi jam internal pada input jam sistem, menjaga nilai CU sama dengan yang diterima dari osilator. Jika CU tidak ditentukan, penganalisis akan menyetelnya ke beberapa nilai default, misalnya, Quartus menyetelnya ke 20 ps. Dalam kasus umum, istilah ini memberi tahu kita bahwa lebih baik menggunakan osilator yang sangat stabil dengan sedikit ketidakstabilan untuk clocking. Osilator yang baik berada di urutan 20-60 ps.

Istilah periode menunjukkan bahwa cara yang jelas untuk memerangi penyesatan transmisi data adalah dengan mengurangi frekuensi clock. Hal ini wajar, tetapi tidak selalu dapat diterima, karena kerangka acuan biasanya memerlukan beberapa kinerja sistem, yang di bawah ini tidak mungkin dijelaskan. Dan kinerja secara langsung bergantung pada kecepatan clock. Kita juga dapat melihat perbedaan antara preset dan hold slack - hold slack tidak bergantung pada frekuensi.

Dan terakhir, istilahnyapada dasarnya mencirikan efisiensi kode tertulis. Oleh karena itu, cara utama untuk menyelesaikan masalah slack adalah menulis ulang dengan benar. Waktu yang tepatmuncul dalam desain perangkat keras yang terlalu kompleks yang membutuhkan terlalu banyak logika kombinasional. Jika Anda memiliki konstruksi yang kompleks dalam proyek Anda, maka cara klasik untuk menyelesaikan masalah ini adalah dengan membagi satu transfer r2r yang kompleks menjadi beberapa transfer sederhana dengan memasukkan 1-2 register lagi ke dalam urutan operasi. Dalam hal ini, penundaan siklus operasi akan meningkat, tetapi kecepatan operasi akan meningkat. Misalnya, menambahkan beberapa vektor dalam satu siklus clock bukanlah ide yang bagus. Lebih baik menambahkan beberapa vektor satu per satu, dengan jumlah antara. Kadang-kadang tidak mungkin untuk memecah beberapa konstruksi kompleks menjadi pipa dari beberapa konstruksi sederhana - maka logika seperti itu harus ditulis ulang dengan cara yang berbeda secara fundamental.

Kesimpulan

Inti dari artikel ini adalah untuk mempelajari tentang keberadaan konsep kendur dan secara fisik bergantung pada apa. Mengetahui hal ini, Anda dapat mempelajari laporan penganalisis batasan waktu secara mandiri, menarik kesimpulan, dan men-debug kinerja proyek Anda. Ini adalah rumus-rumus yang hampir tidak perlu Anda hitung secara nyata. Anda bahkan tidak perlu mengingatnya dengan hati. Penting untuk memahami logika dari apa yang terjadi dalam transfer antar-registrasi dan memahami faktor-faktor apa yang menentukan kecepatan proyek.