tidak, ceritanya dimulai pada 2015, ketika saya berkenalan dengan FPGA. Dalam karya-karya sederhana pertama saya, saya membentuk jam yang saya butuhkan dari konter dan memasukkan semua logika darinya (asalkan, saya membutuhkan jam lebih lambat daripada diumpankan ke FPGA, misalnya UART dan SPI). Secara alami, mereka mengejar saya untuk ini, tetapi saya punya alasan sederhana "tapi berhasil!", Dan semuanya benar-benar berhasil. Sejak itu, pikiran itu merayap di kepala saya: "Di mana saya bisa mendapatkan sinyal waktu?"

Tidak banyak pilihan sumber untuk dicabik-cabik. Baik mengambil dari ClockWizard tertentu berdasarkan PLL atau MMCM, atau membentuknya dari counter, atau langsung dari kaki, sehingga bisa dikatakan, tunggal berakhir. Bagaimana jika kita mengambil sinyal clock yang dihasilkan oleh primitif FPGA?

Sebagai bagian dari artikel ini, saya memutuskan untuk mempertimbangkan tiga opsi: multiplexer (MUXF7), tabel kebenaran (LUT1) dan hubungan pendek kaki FPGA untuk diri mereka sendiri.

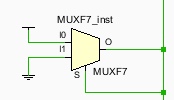

Dalam kasus multiplexer, output diumpankan ke sinyal kontrol, dan sinyal input ditarik ke 0 dan 1.

Dalam kasus LUT, kami melakukan hubungan arus pendek output ke input dan mengatur tabel kebenaran pembalik. Saat memasok "1", output nol, dan saat memasok "0", output satu.

Dalam kasus GPIO, semuanya sederhana di sana, sinyal output ditetapkan kebalikan dari sinyal input:

| menetapkan s2 = ~ s1; |

Tujuan percobaan: untuk menghasilkan frekuensi dalam tiga cara dan mengukurnya.

Kami akan mengukur frekuensi dengan mengorbankan penghitung. Akan ada 4 penghitung: tiga untuk setiap opsi dan satu penghitung dasar, relatif yang semuanya akan dihitung. Dan kita akan menonton penghitung ini melalui ChipScope.

Dan di sini adalah seluruh kode modul:

module gen_clk(

input clk_base,

input s1, //gpio

output s2 //gpio

);

// -

assign s2 = ~s1;

wire clk_gpio = s1;

reg [31:0] cnt_gpio = 0;

(* MARK_DEBUG="true" *) reg [31:0] cnt_gpio_buf = 0;

always@(posedge clk_gpio)

begin

if(cnt_gpio[2:0]==3'd0) cnt_gpio_buf<=cnt_gpio;

cnt_gpio <= cnt_gpio + 1'b1;

end

//

wire clk_mux;

MUXF7 MUXF7_inst

(

.O(clk_mux),

.I0(1'b1),

.I1(1'b0),

.S(clk_mux)

);

reg [31:0] cnt_mux = 0;

(* MARK_DEBUG="true" *) reg [31:0] cnt_mux_buf = 0;

always@(posedge clk_mux)

begin

if(cnt_mux[2:0]==3'd0) cnt_mux_buf<=cnt_mux;

cnt_mux <= cnt_mux + 1'b1;

end

//

wire clk_lut;

LUT1#(

.INIT(2'b01)

)

LUT1_inst(

.O(clk_lut),

.I0(clk_lut)

);

reg [31:0] cnt_lut = 0;

(* MARK_DEBUG="true" *) reg [31:0] cnt_lut_buf = 0;

always@(posedge clk_lut)

begin

if(cnt_lut[2:0]==3'd0) cnt_lut_buf<=cnt_lut;

cnt_lut <= cnt_lut + 1'b1;

end

//

(* MARK_DEBUG="true" *) reg [31:0] cnt_base = 'd0;

always@(posedge clk_base)

begin

cnt_base <= cnt_base + 1'b1;

end

endmodule

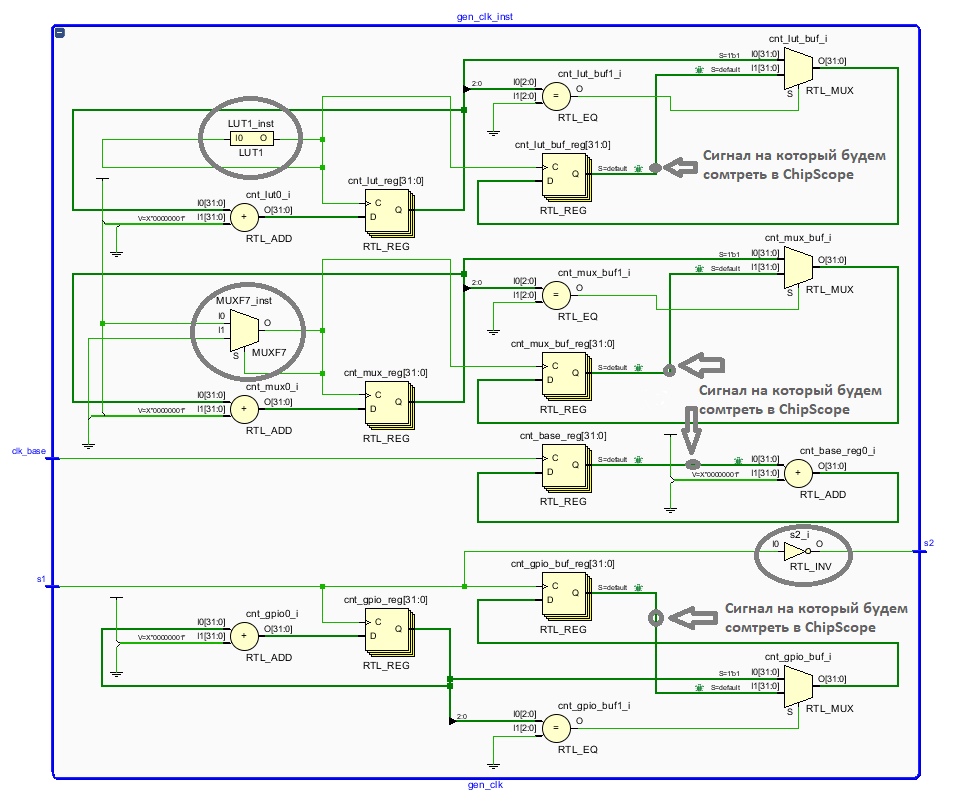

Berikut adalah skema proyek. Primitif dilingkari, dan panah menunjukkan sinyal yang akan dimasukkan ke dalam ChipScope untuk analisis frekuensi:

Bagian praktis Saya

memiliki tiga papan yang saya miliki:

- Kit Evaluasi KC705

- Paket Evaluasi ML507

- Papan Spartan-6 XC6SLX16 Cina

Melihat ke depanKe depan, saya akan mengatakan bahwa papan terakhir tidak memiliki hasil yang normal.

Dan sekarang hasilnya aktual

Kintex-7:

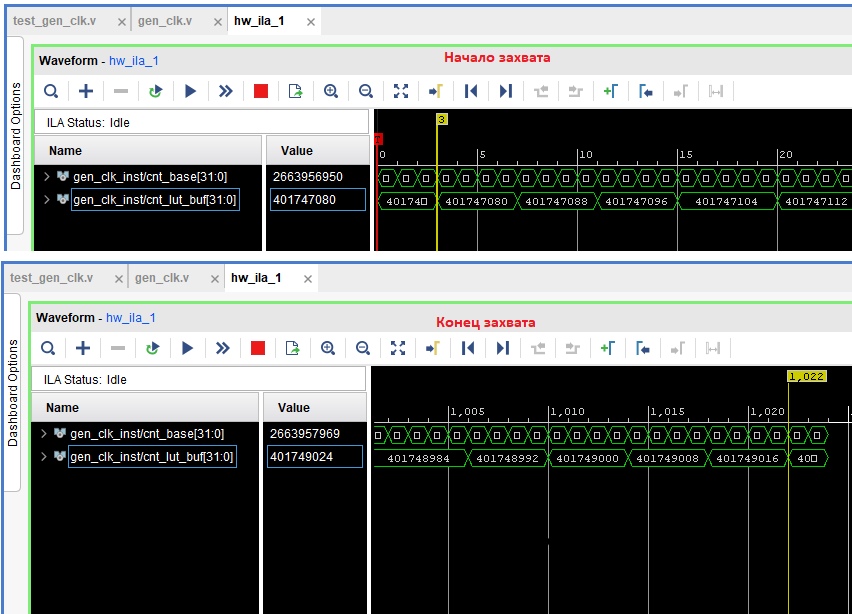

Karena proyek mulai dibuat untuk itu, proyek itu tidak ditulis seluruhnya sekaligus, tetapi secara bertahap. Pertama, saya menghubungkan satu LUT, menambahkan sinyal ke debugging dan mulai menonton.

Penghitung dasar clock pada 200 MHz, sehingga tidak sulit untuk menghitung frekuensi jam yang dihasilkan pada loot, berapa kali penghitung delta penghitung loot adalah delta penghitung dasar pada saat yang sama, begitu sering frekuensinya. Dalam hal ini: frekuensi yang dihasilkan oleh rampasan adalah 381,55 MHz.

Sekarang kita akan menambahkan multiplexer ke proyek, dan dengan analogi dengan satu jarahan, kita akan menghitung frekuensinya, dan untuk jarahan (toh, sesuatu harus berubah).

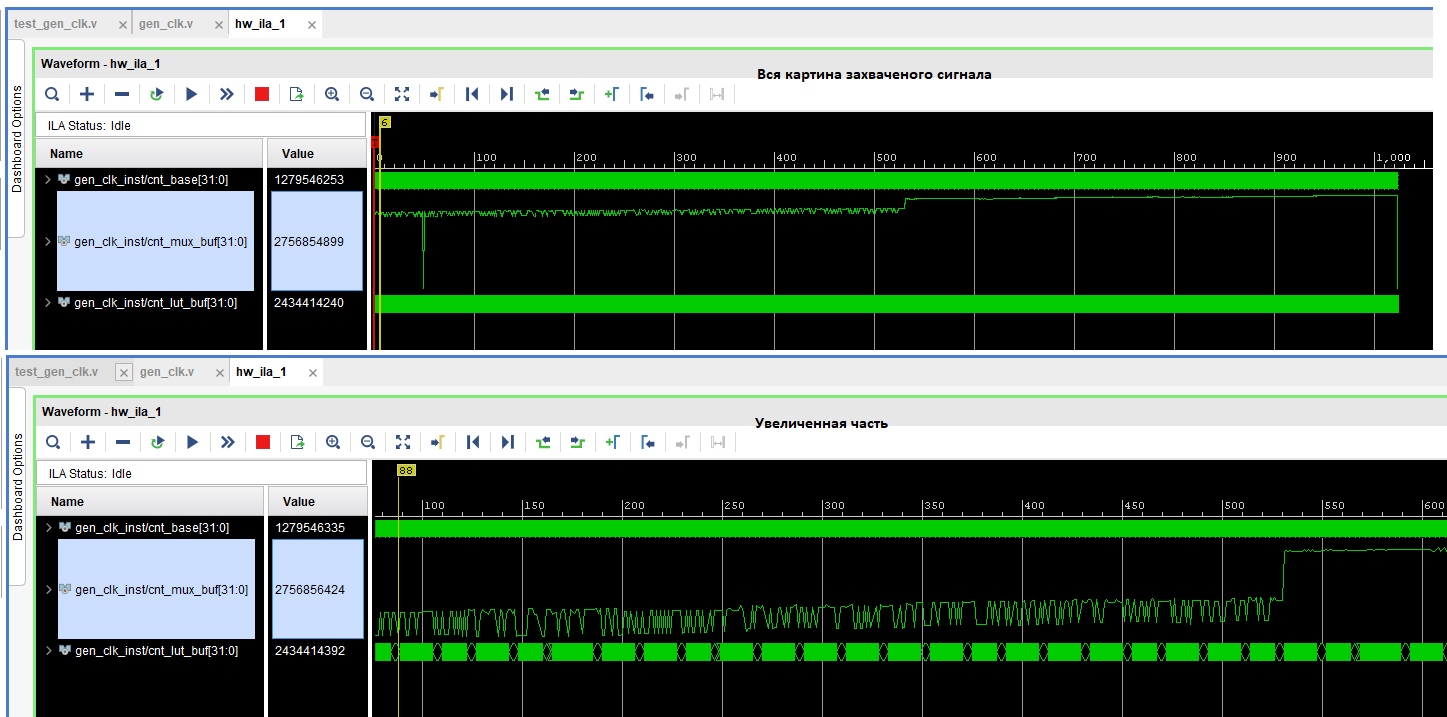

Hal pertama yang menarik perhatian adalah seberapa banyak penghitung bergetar. Ini tercermin dalam frekuensi multiplexer yang sangat besar, tetapi secara umum jelas bahwa penghitungnya meningkat, yang berarti ia juga dapat diambil dan dihitung. Akhirnya:

- Frekuensi multiplexer: 5953,89 MHz

- Frekuensi rampasan (diubah): 379,98 MHz

Nah, pada akhirnya, mari tambahkan loop tertutup dari pasangan GPIO ke proyek. Papan KC705 memiliki konektor SMA J13 dan J14. Di sini saya menutupnya dengan konduktor sepanjang 10 cm. Hasilnya:

- Frekuensi GPIO: 90,59 MHz

- Frekuensi multiplexer: 12994,13 MHz

- Frekuensi rampasan: 380,18 MHz

Mari kita ganti, demi eksperimen, konduktor dengan konduktor yang lebih panjang, saya memiliki kawat dua kali lebih panjang. Akibatnya, frekuensinya turun menjadi 85,29 MHz.

Pada tahap percobaan ini, dapat dicatat bahwa frekuensi operasi primitif di FPGA tidak sama. Dalam kasus ketika hanya ada satu jarahan, maka synthesizer memilih jarahan tercepat dan membangun sirkuit di sekitarnya, kemudian ketika multiplexer ditambahkan, synthesizer mencoba menemukan posisi super di mana rampasan dan multiplexer bekerja secepat mungkin, dan ini adalah elemen dan frekuensi lain yang sudah lebih lambat. Ketika pin eksternal ditambahkan, seluruh proyek pada kristal pada dasarnya dipindahkan ke kaki ini dan proyek mulai disintesis pada elemen terdekat, untuk beberapa alasan, di tempat itu, frekuensi rampasan dan multiplexer meningkat secara nyata, tetapi jangan lupa bahwa dengan latar belakang semua ini, untuk proyek sebuah ChipScope dengan kedalaman 1024 dan bus data dari 64 ke 128 terhubung (itu berubah dari proyek ke proyek). Sekarang mari kita beralih ke papan berikutnya.

Virtex-5:

Saya tidak pergi jauh seperti yang saya lakukan dengan papan sebelumnya, saya segera menambahkan semua 3 opsi untuk menghasilkan jubah dan melihat di ChipScope apa yang terjadi.

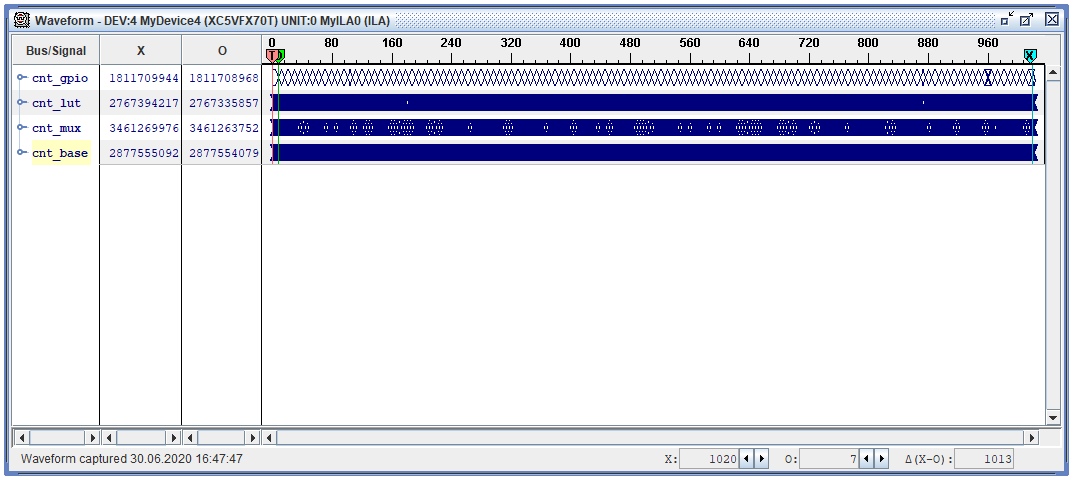

Gambar menunjukkan dua label X dan O. Selain nilainya dalam kolom, format angka adalah desimal yang tidak ditandai. Perlu dicatat bahwa penghitung dasar sekarang dihitung pada 100 MHz. Dan hasilnya:

- Frekuensi GPIO: 96,34 MHz

- Frekuensi multiplexer: 614,41 MHz

- Frekuensi rampasan: 5761.1 MHz

Dapat dilihat bahwa pada papan ini, hasil rampasan ternyata lebih cepat daripada multiplexer, dan frekuensi pin ternyata lebih tinggi daripada pada papan pertama, mungkin ini karena saya menghubungkan kedua pin bukan dengan konduktor 10 cm, tetapi dengan jumper, akibatnya, saluran komunikasi menjadi lebih pendek, dan frekuensinya lebih tinggi.

Dan sekarang opsi terakhir dengan papan Cina.

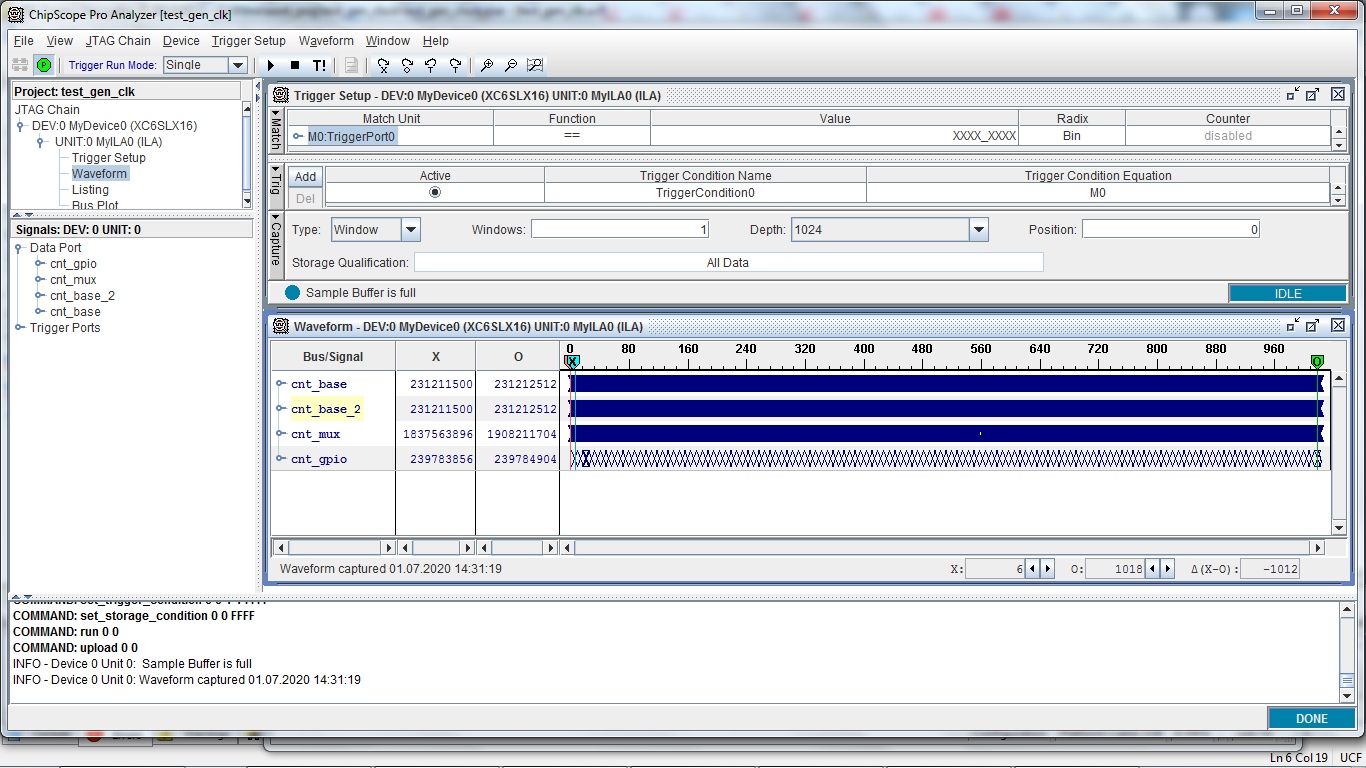

Spartan-6:

Ada dua penghitung dasar di ChipScope, sebenarnya penghitung yang sama tidak ingin mengkonfigurasi ulang ChipScope. Dalam proyek ini, penghitung dasar clock pada 50 MHz.

Dalam hal dewan ini, semuanya ternyata jauh lebih rumit. Pertama, proyek tidak ingin disintesis dengan cara apa pun dalam bentuk yang disintesis dalam versi sebelumnya. Kedua, pada akhirnya, saya harus membuang LUT, saya mencoba menggantinya dengan yang lima arah, tetapi tidak berhasil juga. Secara umum, berikut hasilnya:

- Frekuensi GPIO: 51,77 MHz

- Frekuensi multiplexer: 3 490 504 MHz

- Frekuensi rampasan: gagal dikumpulkan

Hasil dalam kinerja papan ini ternyata sama sekali tidak bahagia, dan bukan hanya karena hasil curian tidak dapat digunakan sebagai bongkahan, tetapi juga karena frekuensi multiplexer yang sangat besar. Adapun kerusakan yang dihasilkan pada kaki, konduktor sekitar 25-30 cm digunakan, pada akhirnya ditutup dengan kawat, kapasitansi parasit dan induktansi mungkin terbentuk di sana, yang memiliki efek pada generasi rusak.

Kesimpulan

Secara umum, kami berhasil membuat sinyal clock pada berbagai primitif, dan kami juga berhasil melihat (menggunakan Kintex-7 sebagai contoh) bahwa primitif memiliki latensi berbeda tergantung pada lokasinya. Atas nama saya sendiri, saya ingin menambahkan bahwa saya tidak menganggap percobaan yang dilakukan sepenuhnya benar, misalnya, lebar bit dari penghitung tidak dihitung, transfer sinyal dari domain pencatatan jam kerja yang berbeda tidak diperhitungkan (meskipun saya membuat sinyal di buffer tetap selama beberapa siklus clock), ChipScope itu sendiri idealnya harus dihapus dan cara lain harus ditemukan menganalisis frekuensi yang dihasilkan.

Masalah yang ditemui:

Vivado ISE , . :

- set_property ALLOW_COMBINATORIAL_LOOPS TRUE [get_nets -of_objects [get_cells gen_clk_inst/LUT1_inst]]

- NET «s1» CLOCK_DEDICATED_ROUTE = FALSE;